## Formal Verification Adoption Made Easy JasperGold Apps and Design RTL-Bring Up

Alexandre Botelho – Application Engineer September 2021

When is your design ready to handoff to verification?

RTL Design Bring-Up Challenges

An advanced design bring-up methodology using JasperGold® Platform

cādence

When is your design ready to handoff to verification?

RTL Design Bring-Up Challenges

An advanced design bring-up methodology using JasperGold<sup>®</sup> Platform

cadence

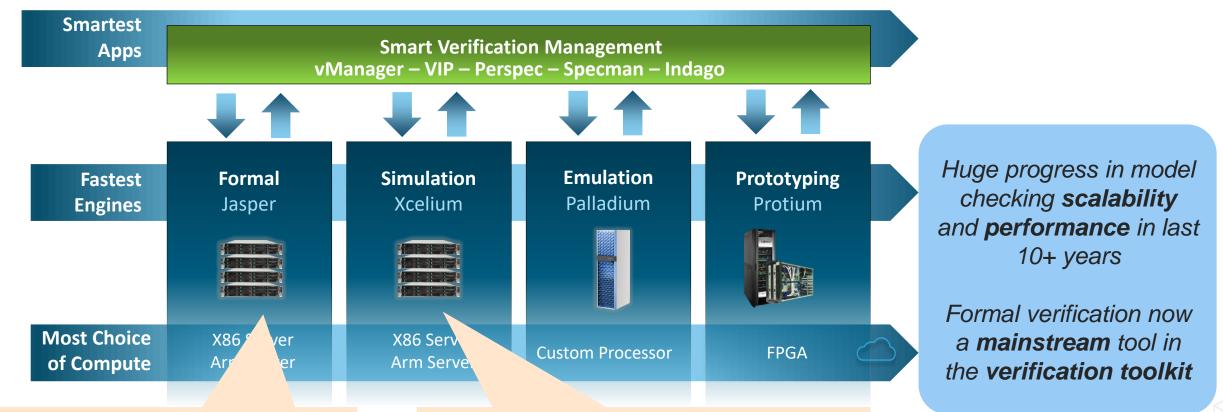

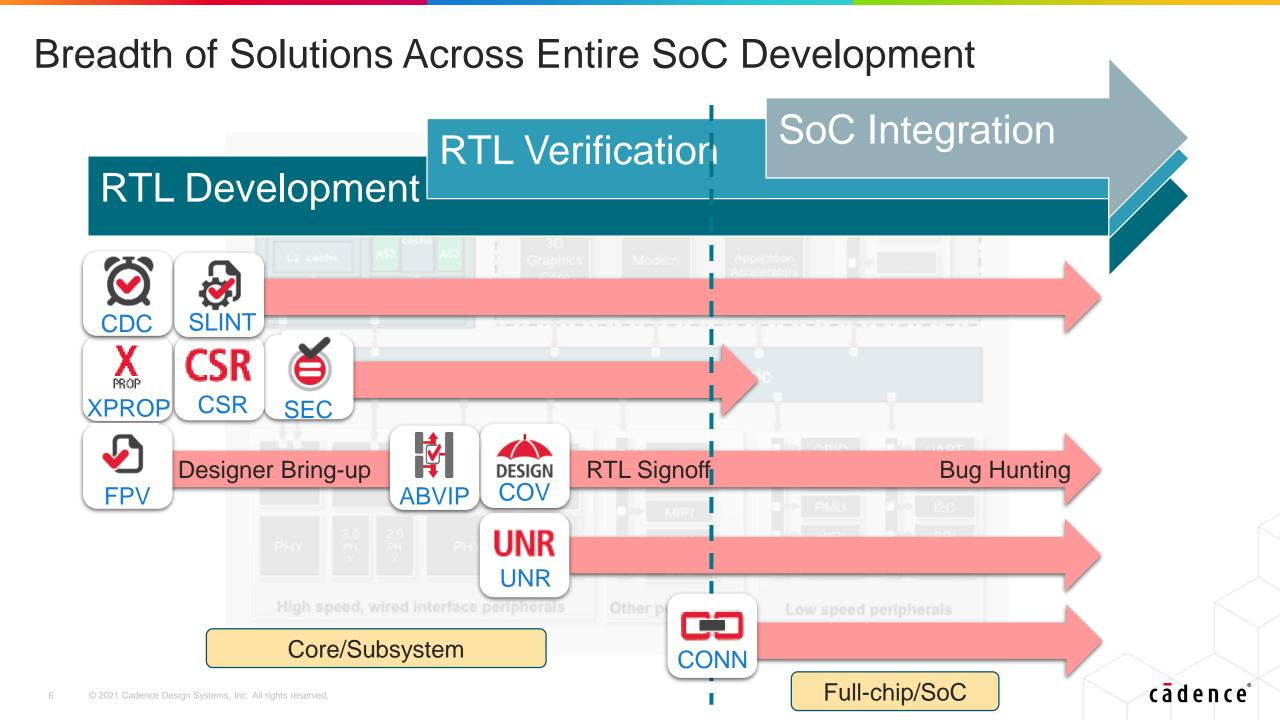

#### Formal: A Key Component for Verification Throughput

#### Find and fix the most bugs per \$ invested in bare metal compute

- Mathematically proves properties

- Automatically exercises all input combinations without a testbench

- Helps verification to "shift left"

- Historical limitation: scalability beyond block/IP level

- Tests based on dynamic stimulus and checkers

- Testbench quality controls verification

effectiveness

- Some directed tests early, full testbench later

cādence

Scales well to block/IP and integration tests

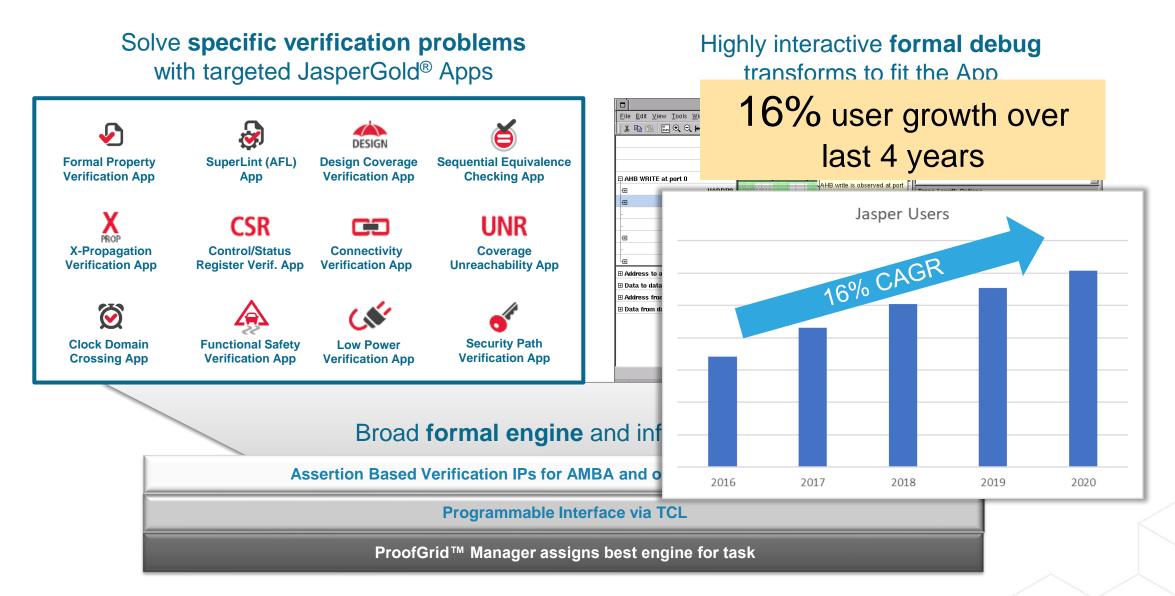

#### JasperGold: Easiest Formal Verification to Adopt

cādence

When is your design ready to handoff to verification?

RTL Design Bring-Up Challenges

An advanced design bring-up methodology using JasperGold® Platform

cādence

#### When is your design ready to hand-off to verification?

- Linting passes a predetermined baseline

- No basic structural problems

- Initialization looks correct

- No unexpected X behavior coming out of reset

- Each line of RTL is reachable (or waived)

- No surprises later with system-level coverage

- Interfaces are clean...no protocol violations

- Our DUT communicates correctly with other blocks

- All specific configuration modes are covered

- Our DUT can be configured into desired modes of operation

- Critical good behaviors can be covered

- No failing Generic Functional Behaviors

- Checks for fundamental behaviors (Ex. overflow, deadlock) are not failing

- Waivers have been saved off

- Our waivers allow us to track what we've already looked at

- User Interface Properties have been exported

- Our interface properties will be double-checked at the system level

#### cādence°

When is your design ready to handoff to verification?

**RTL Design Bring-Up Challenges**

An advanced design bring-up methodology using JasperGold® Platform

cādence

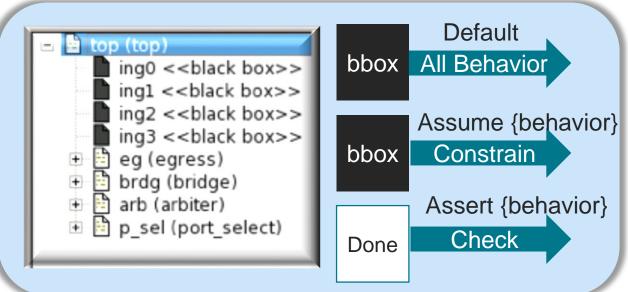

## Bring-Up Challenge #1: Missing Pieces

- Traditional Bring-Up

- You may not have all of the RTL completed, or it doesn't compile yet

- Modeling these low level instances takes a lot of time and is prone to error

- This modeling is often throw-away work and usually not verified in any way

- 10 © 2021 Cadence Design Systems, Inc. All rights reserved.

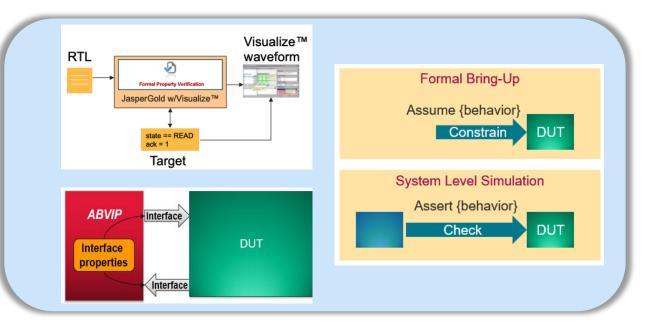

- Formal Bring-Up

- Missing modules can be black-boxed. By default, blackbox outputs allow all possible output behaviors

- Optional assumptions can be added to blackbox outputs to constrain behavior

- When the instance becomes available, the Assumptions can be changed to Assertions to check the behavior

cādence

## Bring-Up Challenge #2: Stimulus

- Traditional Bring-Up

- You spend lots of time trying to inject the correct stimulus for each test

- It is time consuming to generate stimulus that is protocol-compliant

- Stimulus used at the block level is never "double-checked" at the system level

- Formal Bring-up

- Choose the target behavior you want to see and formal creates the stimulus for you

- Leverage Protocol-compliant constraints & checks that may be available for common interfaces (Ex. Cadence Assertion-Based Verification IP)

- Any SVA you use to constrain your DUT can be verified at the system-level, and can also check the behavior of the upstream block!

cādence

# Bring-Up Challenge #3: Checkers

- Traditional Bring-Up

- You spend lots of time developing checkers and scoreboards

- Each check you perform relies on specific stimulus

- Checkers you create usually provide little value to other RTL developers or the verification team

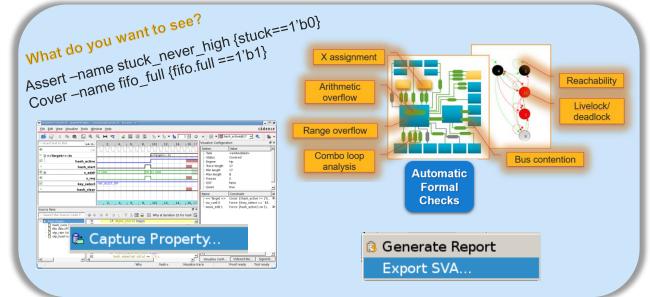

- Formal Bring-up

- No need to worry about the stimulus required to exercise the check. Focus on the end behavior and formal shows you the stimulus required

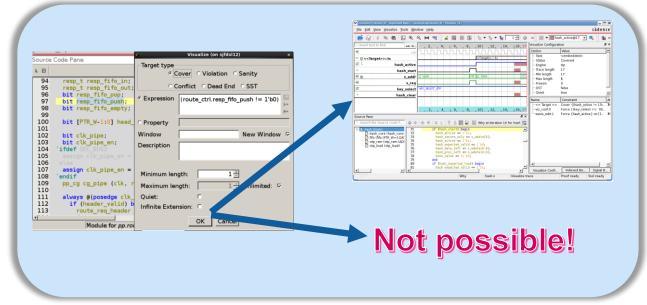

- You may be able to capture checker properties directly from interesting waveforms (Ex. JasperGold<sup>®</sup> Visualize<sup>™</sup>)

- Leverage Automatic Formal checks for generic behavior such as arithmetic overflow, deadlocks and more (Ex. JasperGold<sup>®</sup> Superlint App)

- All checks can be used by the verification team (simulation or formal) and by other designers

#### Bring-Up Challenge #4: Dead Code & Unreachable Behaviors

- Traditional Bring-Up

- You may spend lots of time trying to exercise code and behaviors that are actually unreachable

- Some unreachable behaviors are expected, but you have no way to confirm this with simulation

- Formal Bring-up

- If you ask formal to demonstrate (cover) a behavior, it will either show you a waveform or say it is impossible

- Good behaviors that are not possible could indicate an RTL bug

- You may also be able to leverage automatic formal Deadcode checks (Ex. JasperGold<sup>®</sup> Superlint App)

cādence

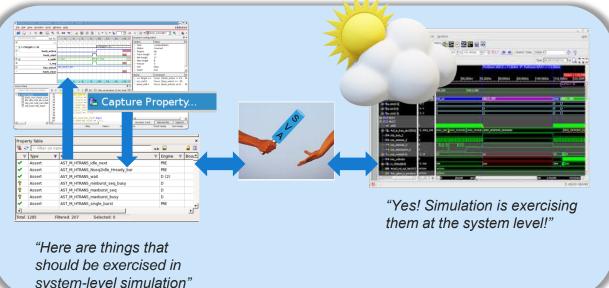

## Bring-Up Challenge #5: Poor Visibility At System-Level

- Traditional Bring-Up

- Once you send your RTL "over the wall", is the verification team exercising things you are concerned about?

- Bug escapes often occur where the system- level tests are not testing what you need them to

- Formal Bring-up

- Behaviors that you visualize during design bring-up are written and captured in the form of SVA properties

- SVA Properties can be handed off to the verification team to give you confidence that these behaviors are also being exercised at the system-level

cādence

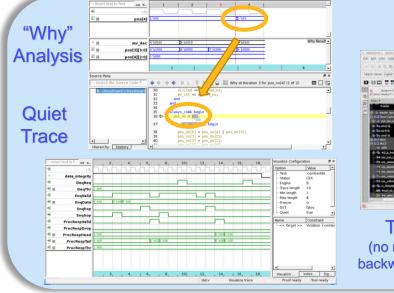

## Bring-Up Challenge #6: Pinpointing The Root Cause

- Traditional Bring-Up

- A unit-level testbench produces failing traces that are much longer than formal traces

- When a failure happens at the systemlevel, root-cause analysis takes much longer

- Which block failed?

- Where is the failure inside the block?

The problem is here! (no more wasted time debugging backwards from the system outputs)

- Formal Bring-up

- During bring-up, formal finds the shortest waveform that shows the behavior, minimizing debug time

- Take advantage of formal tool capabilities you may have to quickly root-cause issues (Ex. JasperGold<sup>®</sup> Visualize "Why" and "QuietTrace")

- Exported SVA properties that you run in systemlevel simulations pinpoint the exact time and location of the behavior

cādence

When is your design ready to handoff to verification?

**RTL Design Bring-Up Challenges**

An advanced design bring-up methodology using JasperGold<sup>®</sup> Platform

cadence

Summary

Q&A

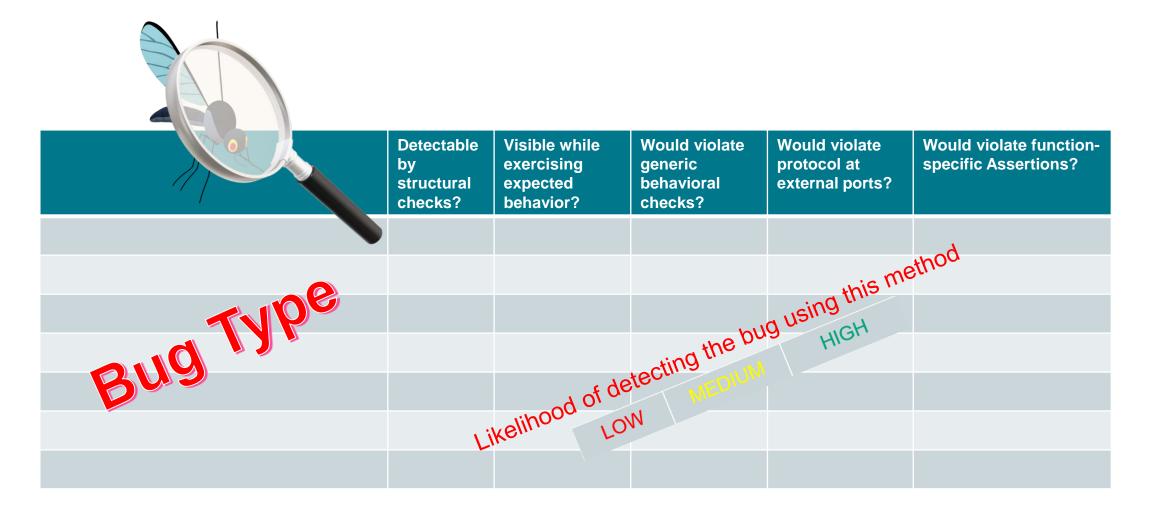

#### Anatomy of various RTL bugs

#### cādence

|                                     | Detectable<br>by<br>structural<br>checks? | Visible while<br>exercising<br>expected<br>behavior? | Would violate<br>generic<br>behavioral<br>checks? | Would violate<br>protocol at<br>external ports? | Would violate function-<br>specific Assertions? |

|-------------------------------------|-------------------------------------------|------------------------------------------------------|---------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| Unconnected internal signal         | HIGH                                      | MEDIUM                                               | HIGH                                              | MEDIUM                                          | HIGH                                            |

| Latched (stuck) signal              | LOW                                       | MEDIUM                                               | HIGH                                              |                                                 | HIGH                                            |

| FIFO push when full                 | LOW                                       | MEDIUM                                               | MEDIUM                                            | HIGH                                            |                                                 |

| Performance bug                     | LOW                                       | HIGH                                                 | LOW                                               | LOW                                             |                                                 |

| Register missing a reset assignment | HIGH                                      | MEDIUM                                               | MEDIUM                                            | MEDIUM                                          | HIGH                                            |

| Out-of-bound indexing               | LOW                                       | LOW                                                  | HIGH                                              | LOW                                             | MEDIUM                                          |

| Corner-case protocol violation      | LOW                                       | LOW                                                  | LOW                                               | HIGH                                            | LOW                                             |

| Unreachable case                    | MEDIUM                                    | MEDIUM                                               | HIGH                                              | LOW                                             | MEDIUM                                          |

| FSM deadlock                        | LOW                                       | LOW                                                  | HIGH                                              | LOW                                             | MEDIUM                                          |

| Function-specific bug               | LOW                                       | MEDIUM                                               | LOW                                               | LOW                                             | HIGH                                            |

# Anatomy of various RTL bugs

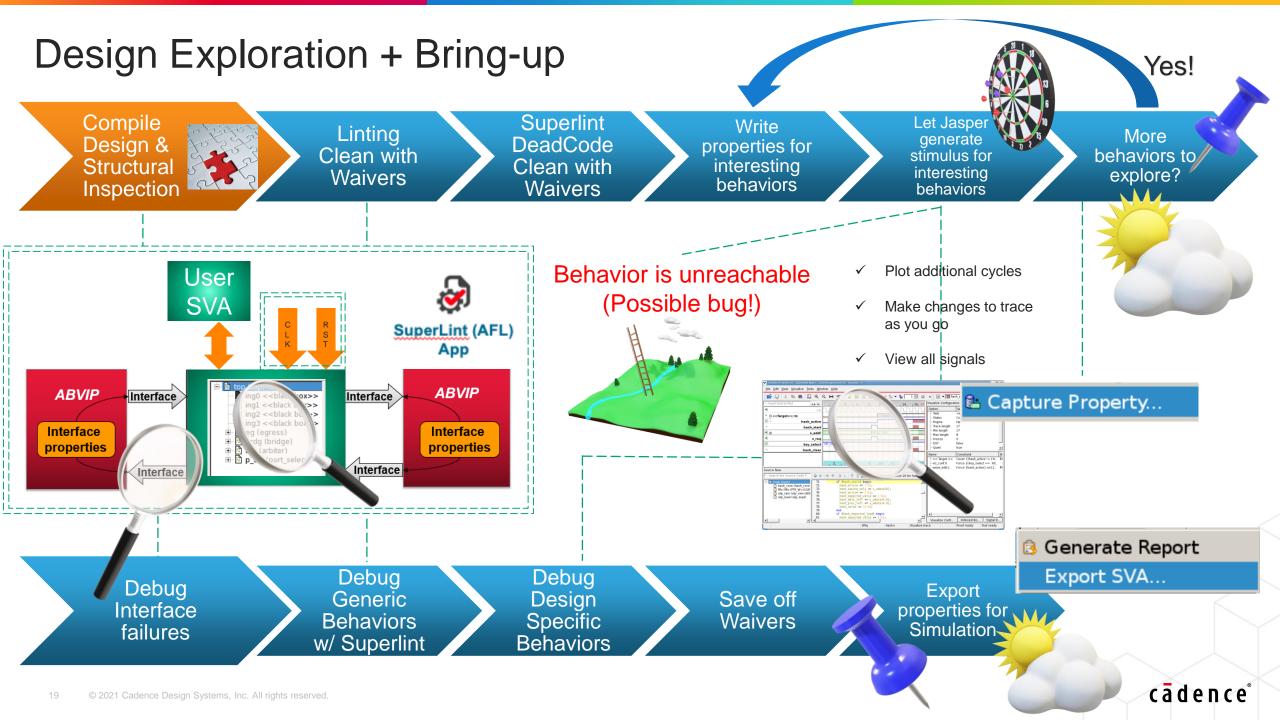

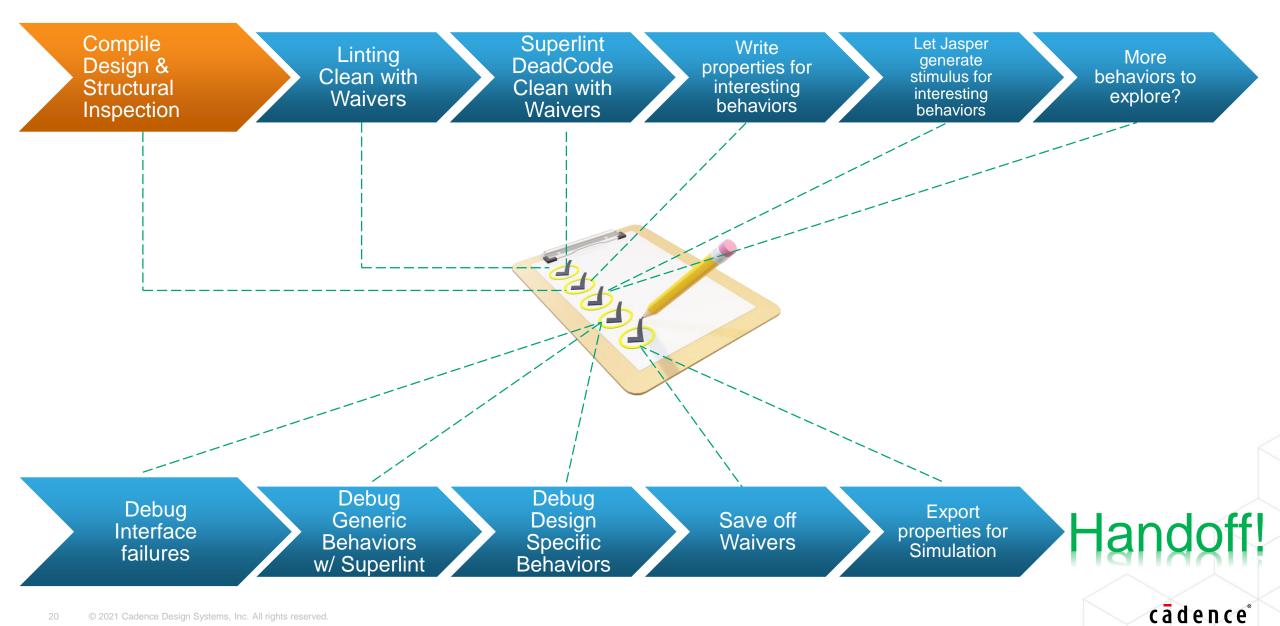

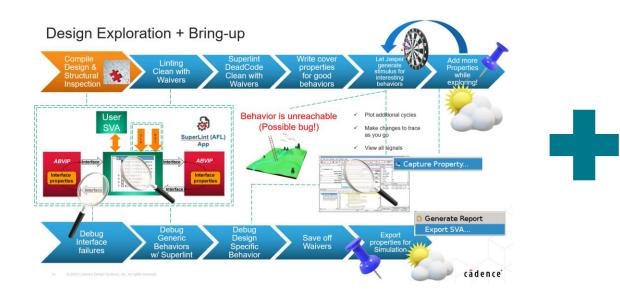

## Design Exploration + Bring-up

When is your design ready to handoff to verification?

RTL Design Bring-Up Challenges

An advanced design bring-up methodology using JasperGold<sup>®</sup> Platform

cādence

- Designers are faced with many challenges when trying to bring-up their designs

- Using a solid methodology combined with cutting-edge formal capabilities, designers can perform design bring-up and address each of these challenges

- By going through each step of the flow, designers can be confident they have addressed each criteria required for handing their RTL over to the verification team

- This design bring-up methodology can replace unit-level simulation while also providing team-friendly capabilities through the use of portable properties

#### What's next?

#### The most comprehensive flow for Designers!

cādence

When is your design ready to handoff to verification?

RTL Design Bring-Up Challenges

An advanced design bring-up methodology using JasperGold® Platform

cādence

#### Questions?

#### My Contact Info

- Alexandre Botelho, Application Engineer

- 。 <u>alexandre@cadence.com</u>

#### Cadence Online Support

- More information about JasperGold Formal Property Verification, JasperGold Superlint and much more!

- Rapid Adoption Kits (RAK's)

- JasperGold RTL Design Bring-Up

- JasperGold Superlint App

JasperGold® Landing Page on Cadence Support Portal!

Find material to answer questions and learn about JasperGold features and formal techniques at <a href="mailto:support.cadence.com/jaspergold\_apps">support.cadence.com/jaspergold\_apps</a>

Rapid Adoption Kits (RAKs) with labs - Application Notes cadence Advanced literation as Uses Fand Van without - Troubleshooting articles Cases Tarls & Restarces Self-serving Scheme My Supp ΔΟ - Videos Amportanti Appo Provide feedback - Training bytes and more! about content ed Asperiot Na and website -Case submission Get answers from support team. When filing ADDER 18.03 Particula LAKE a case, COS will automatically suggest ADDER ALL BARRIER documents that could address query. Anna Tan Dispat Product and units (1) (Inc. 2021 JasperGold-specific search bar Podul suppred Limits search to JasperGold-related content only Rabine unter JasperGold landing Protect Mercury Remote Schedule page organized by Apps! Twing Schedu Each App tab contains App-Left-hand side bar filters the state of the s specific content. material by document type Jesper User Group Conference 2018 Presented JasperGold Technology Update ad Posturia cadence Easy access to JUG Papers and Tech Updates

#### cādence°

# cādence

© 2021 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

# **New!** The Blended/Virtual Training Solution

Combining the best of all our training methods!

- Live lectures conducted by Cadence's expert instructors

- Flexibility—attend the training wherever you are

- **Self-study** lab work with instructor support

- Interactive live Q&A sessions and much more

Visit the **Cadence Training** website:

www.cadence.com/training

#### cādence®

# Cadence Learning and Support System

The one stop shop for all your learning and support needs!

- **Speed your** technical learning!

- All online training is FREE for Cadence customers with a Support account

- Access to hundreds of online courses available through <a href="https://support.cadence.com">https://support.cadence.com</a>

cadence

| You might be interested in this online course:          |            |  |  |  |

|---------------------------------------------------------|------------|--|--|--|

| SVA, Formal & JasperGold®<br>Fundamentals for Designers |            |  |  |  |

| Questions?<br>Reach out to us at <u>eur_training@c</u>  | adence.com |  |  |  |