**Accelerating Verification and Implementation** With Machine Learning for Electronic Design Automation

Frank Schirrmeister, Sr. Group Director, Solutions & Ecosystem DVCLUB, November 23<sup>rd</sup> 2021

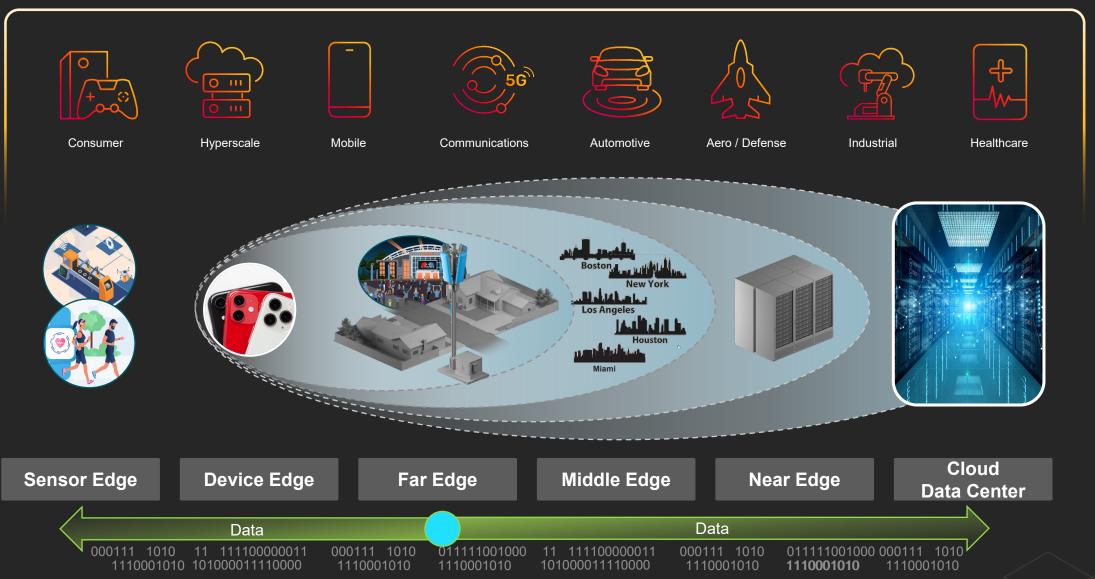

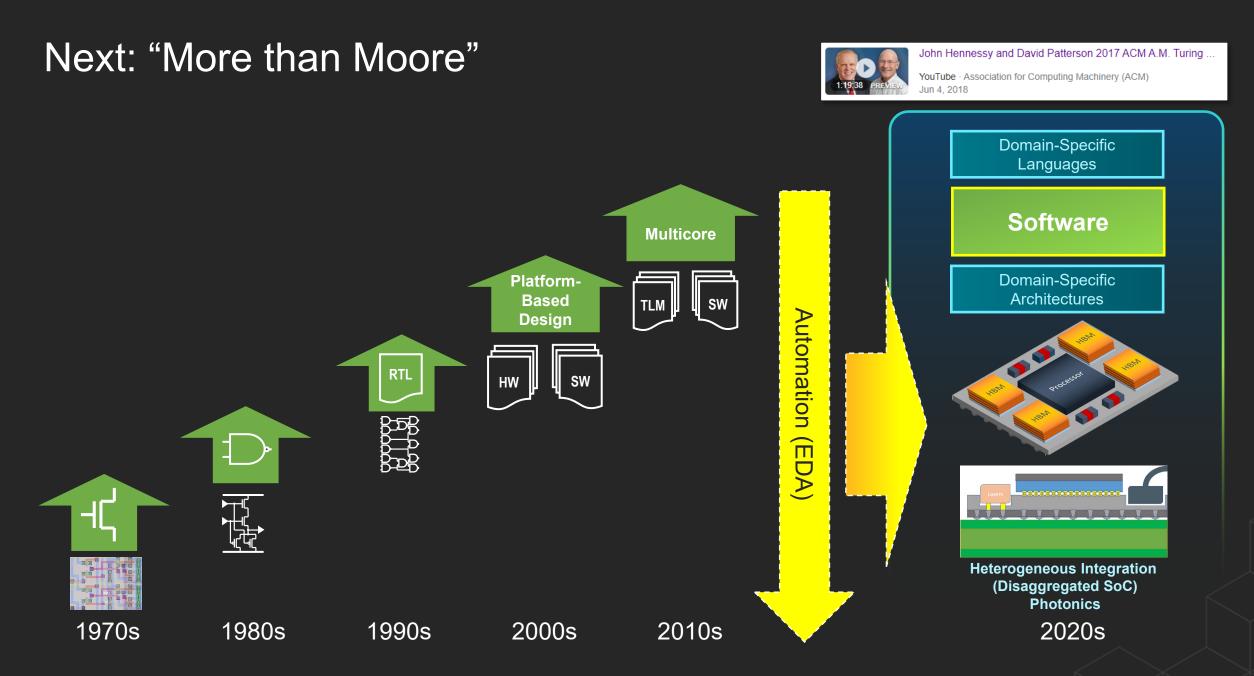

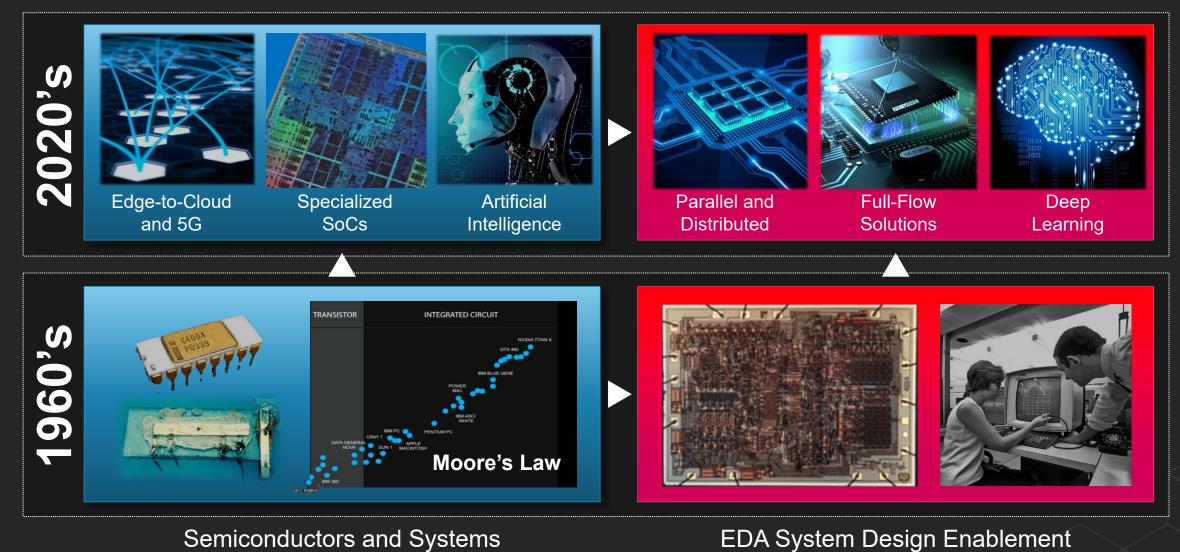

### Intelligent Systems: Ubiquitous Hyperconnectivity

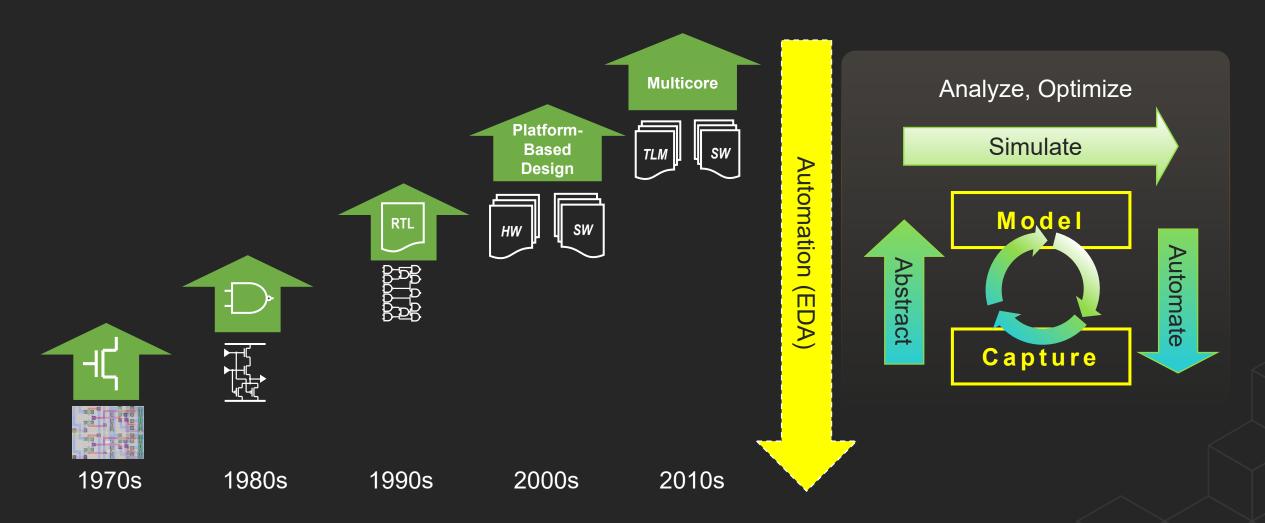

### EDA Enables AI/ML Designs

**IP and Subsystems**

Implementation

**Board and Package**

Systems

IP Selection "Reuse the right building blocks" DSPs, Interfaces, Analog

#### **HW/SW Verification**

**"Is it functionally correct?"** Hardware/Software, Power, Architecture, Safety, Security

#### **Chip Implementation**

"Optimized, advanced-node implementation" Performance, Power, Cost

#### Packaging PCB Integration

"Silicon into packages and parts into PCBs and 3D-IC heterogeneous integration"

#### System Analysis

**"Does it work when put together?"** Electromagnetic, Thermal, Low Power, Computational Fluid Dynamics Optimized flows to enable AI/ML chips and systems (for users)

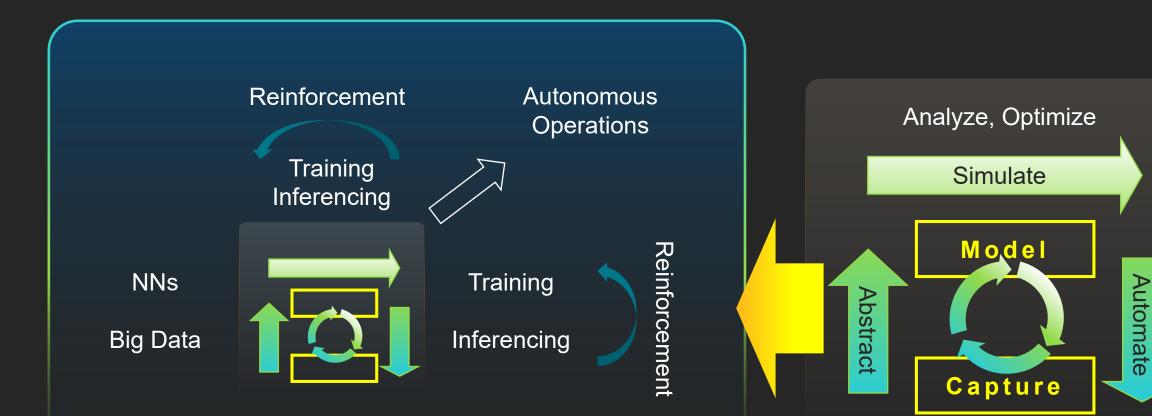

### AI/ML is **Enabling EDA** too!

IP Selection "Reuse the right building blocks" DSPs. Interfaces. Analog

**HW/SW Verification**

**Development productivity**

# Using Al/ML to increase productivity of EDA flows

Board and Package

System Analysis

into Is

Does it work when put together?" ectromagnetic, Thermal, Low Power, Computational Fluid Dynamics Optimized **flows** to **enable AI/ML** chips and systems

IP and Su

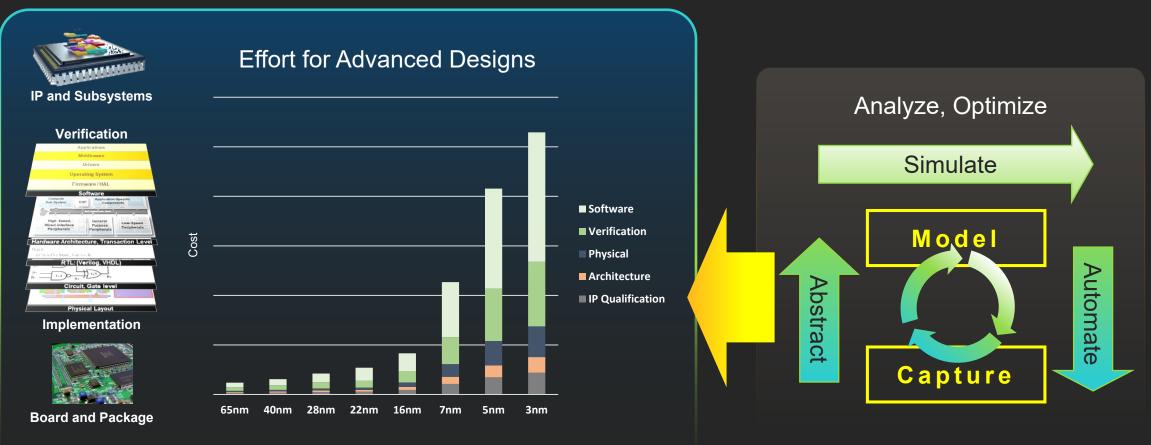

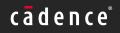

### EDA Keeps Design Cost in Check – Commonalities

| ca | d | e | Ŋ. | C | e |

|----|---|---|----|---|---|

| ca | d | e | ŋ. | C | e |

### Targeting "High Effort" Aspects of the Design Flows

Source Data: IBS 2021, Cadence

cādence<sup>°</sup>

### EDA and AI/ML

7 © 2021 Cadence Design Systems, Inc. All rights reserved.

#### cādence°

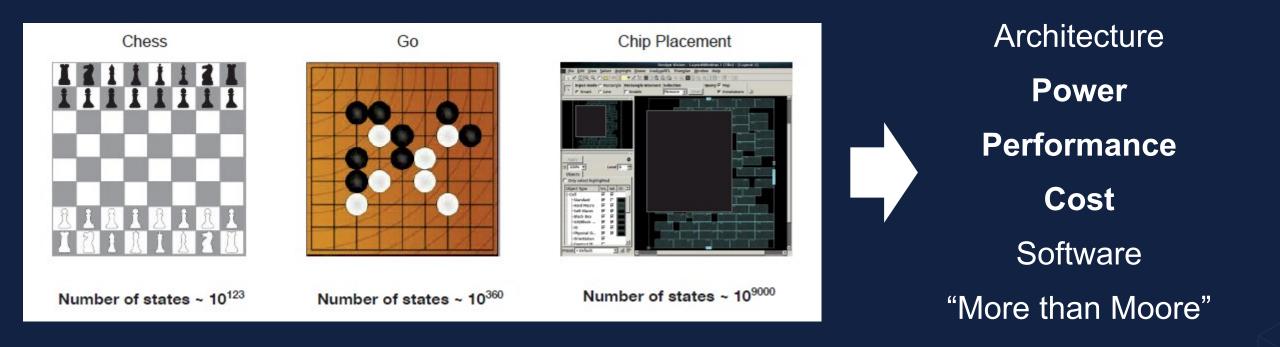

### So You Think Chess & Go Were Complex?

Source: The Next Platform, "Google Teaches AI to Play the Game of Chip Design", <u>https://bit.ly/3Bwxg8p</u>, Cadence

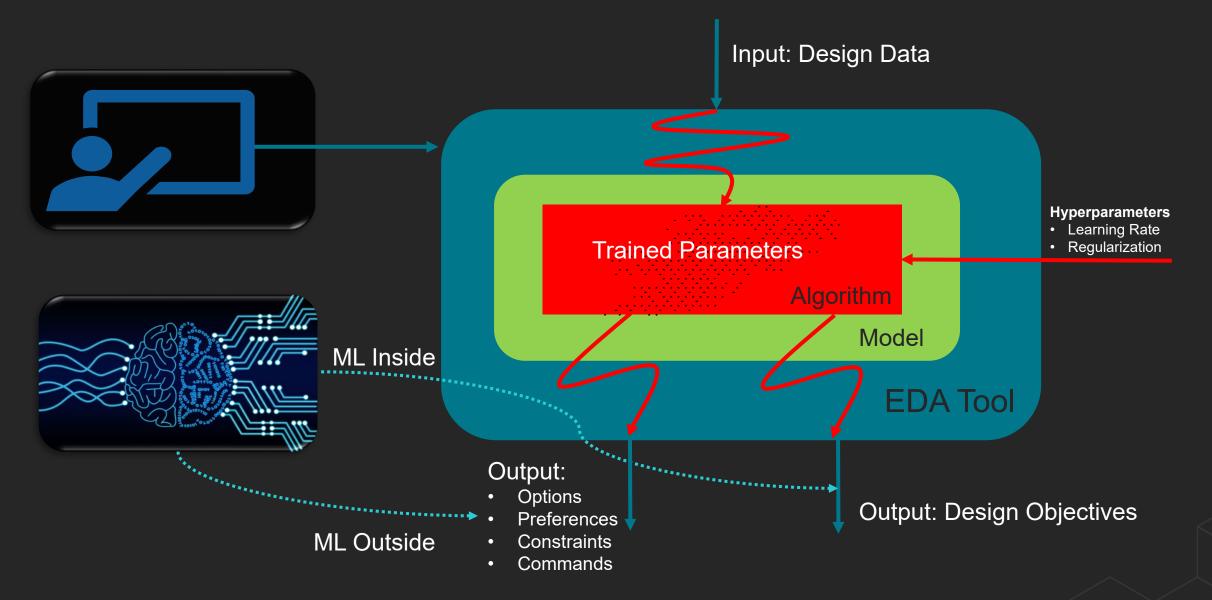

### ML in Electronic Design Automation

#### cādence

### AI/ML Opportunities in EDA

| Functional Verification    | <ul> <li>Simulation smarter and faster regressions</li> <li>Formal verification formal proof orchestration</li> </ul>                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Implementation     | <ul> <li>Digital implementation "ML inside" delay prediction</li> <li>Digital implementation "ML outside" flow optimization</li> </ul>   | IP and Subsystems<br>Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Library Characterization   | • Library characterization with ML-based prediction                                                                                      | Drivers<br>Operating System<br>Firmware (HAL<br>Software<br>Part System<br>With Seed,<br>With S |

| Custom IC Implementation   | <ul> <li>SPICE simulation ML for accurate response surface models</li> <li>Custom implementation: Layout and analog placement</li> </ul> | Hardware Architecture, Transaction Level         Spin         Provide State Stress         Microsoft State Stress         Direction State Stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Design for Manufacturing   | ML-DFM: Predicting unknown yield limiting hotspots                                                                                       | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PCB Synthesis              | • PCB design placement, via, routing, power delivery, analysis                                                                           | Board and Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| System Design and Analysis | • System analysis "Smart Sweep" Predict eye openings                                                                                     | Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

cādence°

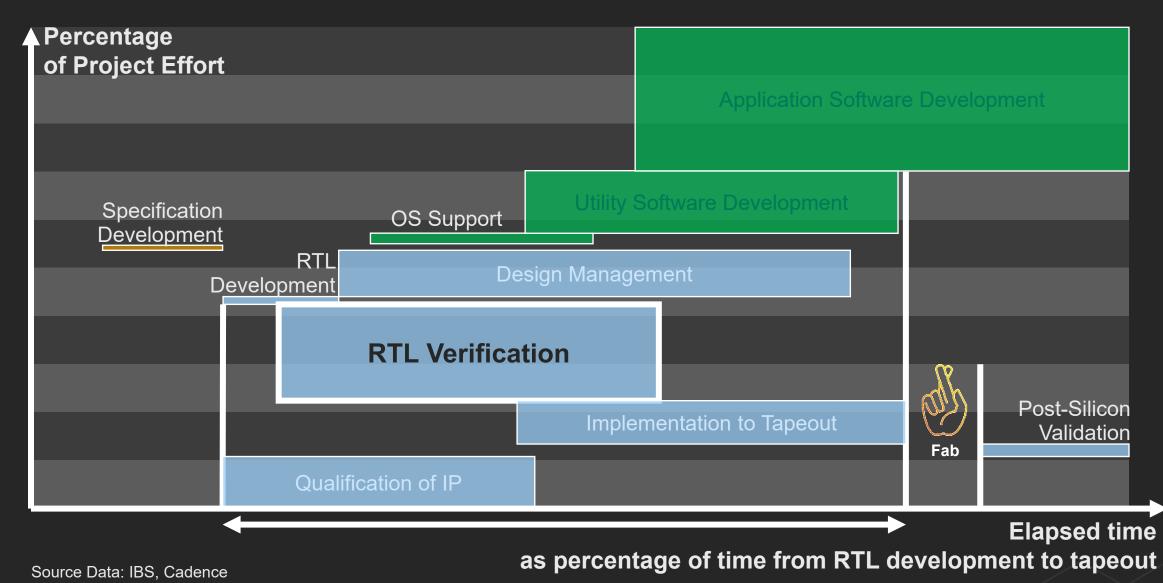

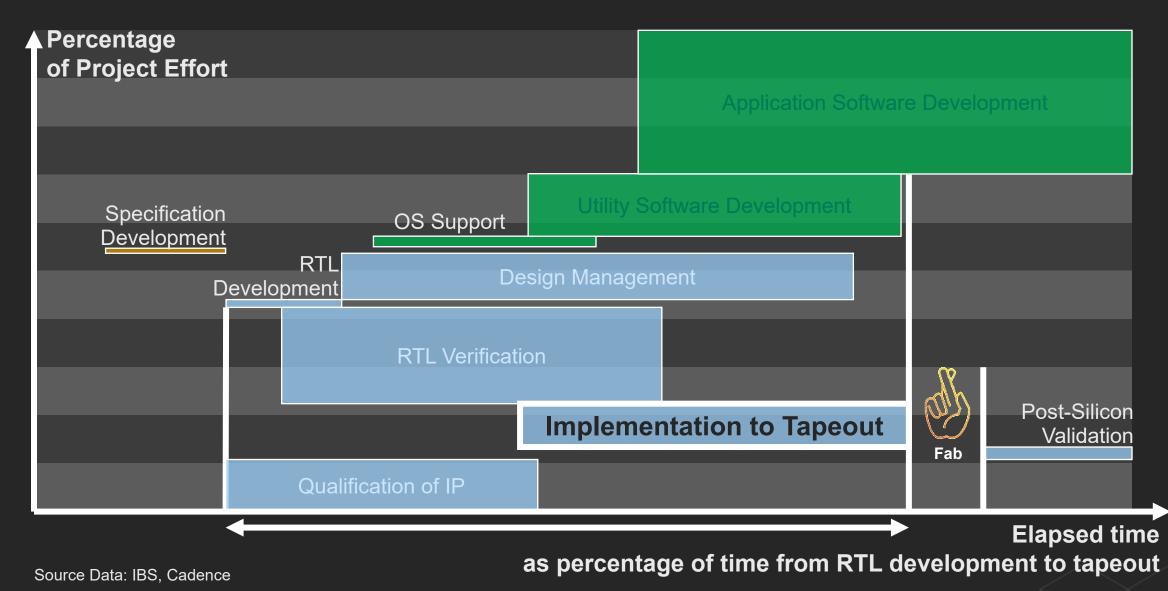

### Verification as Part of Chip Development Efforts

cadence

#### 11 © 2021 Cadence Design Systems, Inc. All rights reserved.

### **ML** in Functional Verification

#### cādence

### **ML** in Functional Verification

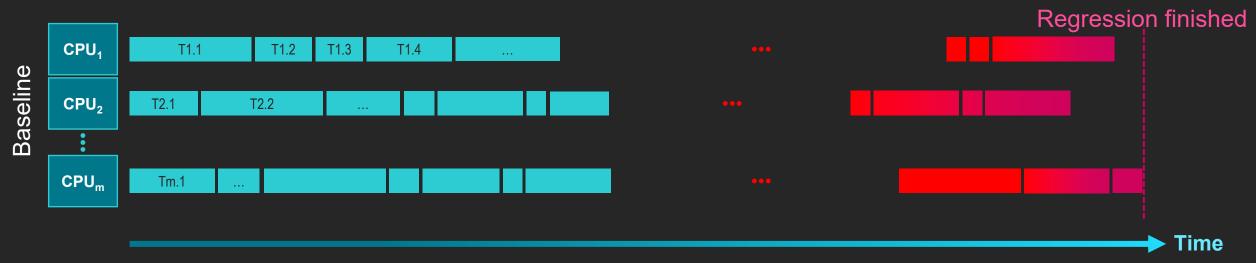

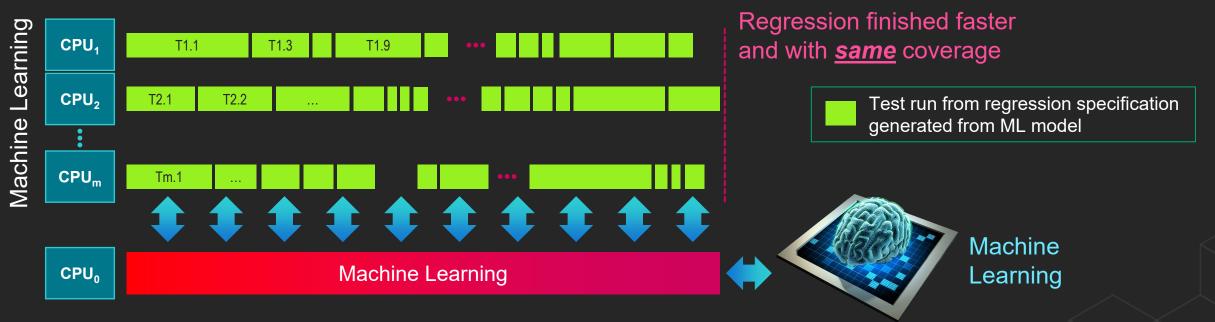

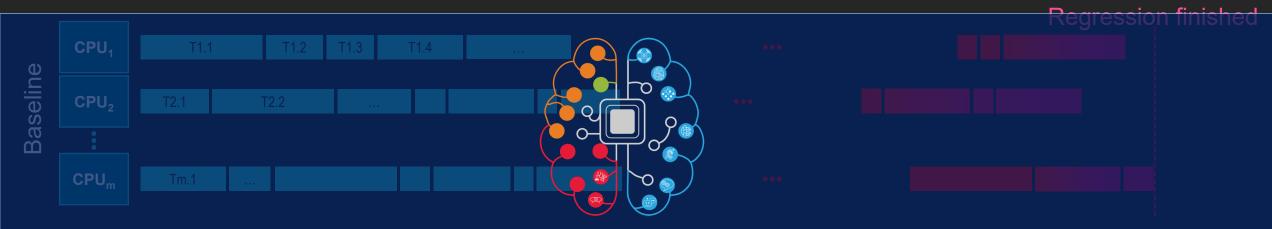

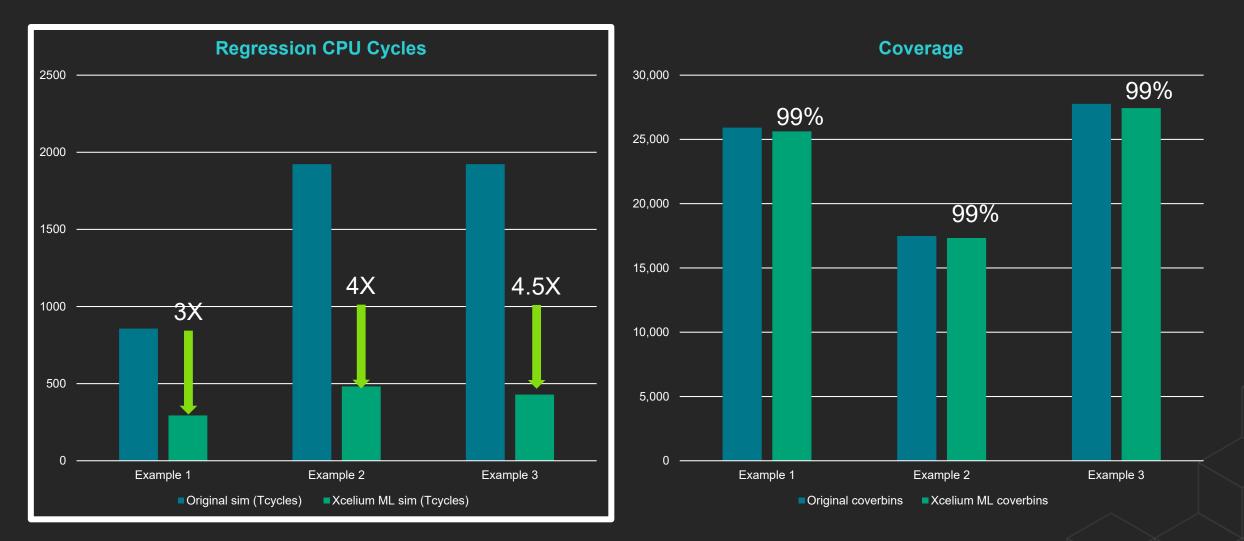

### Xcelium-ML Up to 5x efficiency at same coverage

#### cādence°

### Xcelium ML for Verification Throughput

Xcelium<sup>™</sup> ML Randomized **Test Suite Run** N Up to 5X faster Machine Same coverage Learning **Xcelium ML** Randomized **Test Suite** Run N+1

Kioxia has effectively utilized Xcelium simulation for a variety of our designs, and it addresses our ever-growing verification needs. With the new Xcelium ML, we've seen a **4X shorter turnaround time** in our fully random regression runs **to reach 99% function coverage of original**, and plan to use this technology in production designs to shorten the time to market for Kioxia's business."

#### Kazunari Horikawa

Senior Manager, Design Technology Innovation Division Kioxia Corporation

cādence

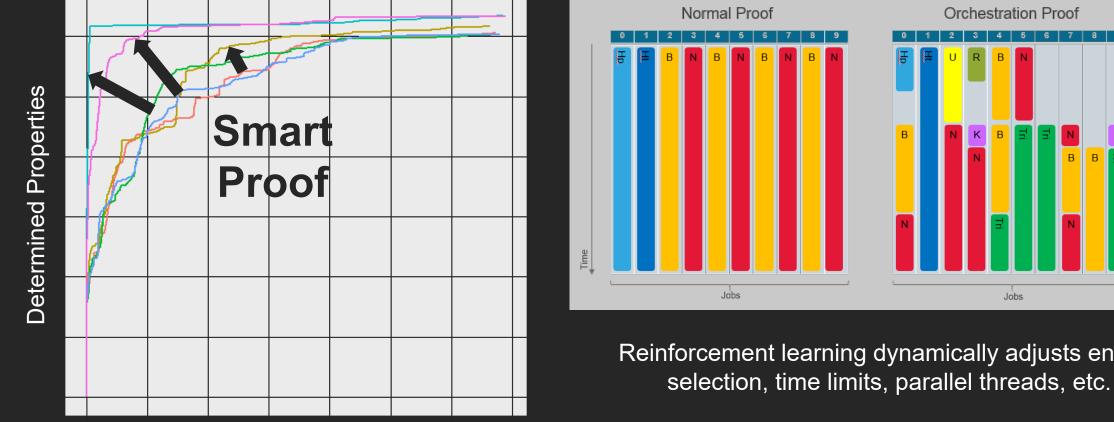

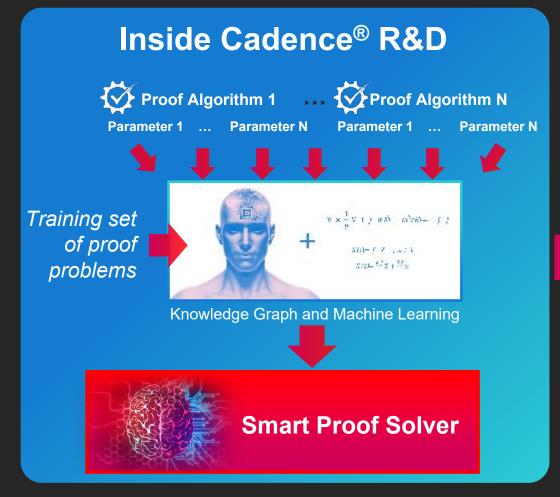

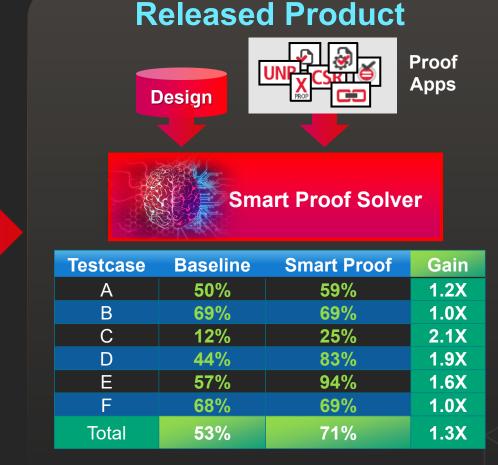

### **Smart Proof in Formal Verification Optimize Resources, Reproduce Previous Runs**

Time

Single-Prop Scans Jobs Reinforcement learning dynamically adjusts engine

**Orchestration Proof**

4 5 6

#### cadence

Initial

scan

### Smart Proof in Formal Verification

Computational logistics technology for formal throughput

#### \* Average results from typical regressions; actual results may vary

### **Smart Proof in Formal Verification**

Computational logistics technology for formal throughput

\* Average results from typical regressions; actual results may vary

### Implementation as Part of Chip Development Efforts

cādence°

ML for Better Performance and Productivity

a

#### **ML Delay Prediction**

- Innovus<sup>™</sup> pre-route delay engine

- Better PPA

- Faster, more predictable results

- ML optimizes delay prediction

- All optimization done on customer data, at customer site

#### **Intelligent Chip Explorer**

- Automated smart design flows

- Productivity improvements

- ML optimizes flow (SI congestions)

- Adjusting tool and library options, constraints, parallel runs in cloud

- All optimization done on customer data, at customer site

cadence

Ö

#### RENESAS

To efficiently maximize the performance of new products that use emerging process nodes, digital implementation flows used by our engineering team need to be continuously updated. **Automated design flow optimization is critical for realizing product development at a much higher throughput.** Cerebrus, with its innovative ML capabilities, and the Cadence RTL-to-signoff tools have provided automated flow optimization and floorplan exploration, improving design performance by more than 10%. Following this success, the new approach will be adopted in the development of our latest design projects.

Satoshi Shibatani, director, Digital Design Technology Department, Shared R&D EDA Division, Renesas

## Summary

22 © 2021 Cadence Design Systems, Inc. All rights reserved

#### cādence°

#### AI/ML Productivity Improvements - Some Examples

**Functional Verification**

**Digital Implementation**

Library Characterization

**Custom IC Implementation**

**Design for Manufacturing**

**PCB** Synthesis

System Design and Analysis

Up to **5X reduction in simulation cycles (**same coverage) Up to **4X** (2X avg.) **better out-of-the-box proofs**

Up 20% better PPA, up to 10X productivity

Accelerated library development Example: 47% of libs interpolated 98%+ pass rate

Accurate **response surface model** of the device or block Layout group prediction

> Hotspot prediction In-design detection and fixing

> > Faster design closure Routability

**Reduction in simulation time**

### AI/ML Productivity Improvements - Some Examples

**Functional Verification**

**Digital Implementation**

Up to **5X reduction in simulation cycles (**same coverage) Up to **4X** (2X avg.) **better out-of-the-box proofs**

Up 20% better PPA, up to 10X productivity

Library Characterization

**Accelerated library development** Example: 47% of libs interpolated 98%+ pass rate

# This is truly just the beginning!

**Design for Manufacturing**

Hotspot prediction n-design detection and fixing

PCB Synthesis

**System Design and Analysis**

aster design closure Routability

Reduction in simulation time

#### cādence

#### Electronics Innovation – An Exiting Future Ahead

#### cādence<sup>27</sup>

# cadence®

© 2021 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks are the property of their respective owners.