# UVVM UVM for VHDL designers – An introduction

DVClub, 28 June 2022

EmLogic.no

The Norwegian Embedded Systems and FPGA Design Centre

- Independent Design Centre for Embedded Systems and FPGA

- Established 1<sup>st</sup> of January 2021. Extreme ramp up

- January 2021: 1 person

- June 2022:  $\rightarrow$  23 designers (SW:8, HW:3, FPGA:10) **And still growing...**

- Continues the legacy from bitvis

- All previous Bitvis technical managers are now in EmLogic

- Verification IP and Methodology provider  $\bigcup \bigvee \bigvee \bigvee$

- Course provider within FPGA Design and Verification

- Accelerating FPGA Design (Architecture, Clocking, Timing, Coding, Quality, Design for Reuse, ...)

- Advanced VHDL Verification Made simple (Modern efficient verification using UVVM)

- A potential partner for ESA projects for European companies

- Increased opportunities due to Norway's low geo return

#### 3 UVVM: UVM for VHDL designers - An introduction

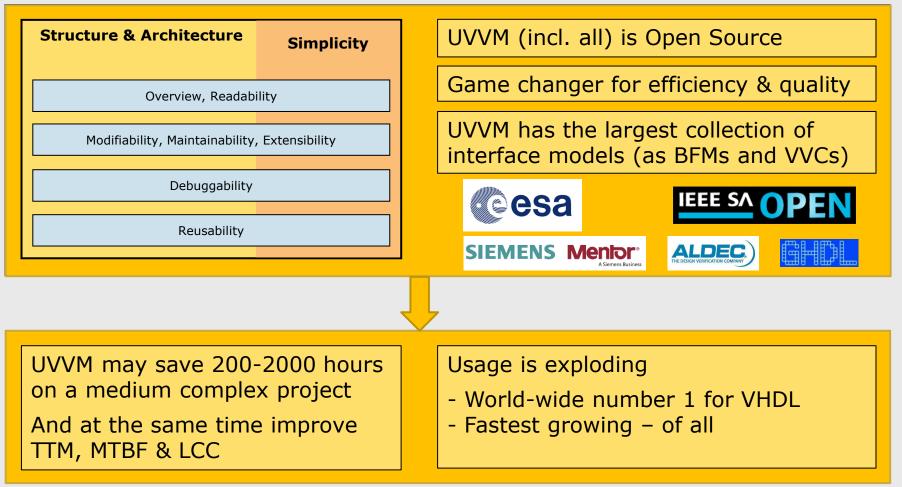

# What is UVVM?

UVVM = Universal VHDL Verification Methodology

- VHDL Verification Library & Methodology

- Free and Open Source

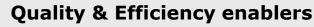

- Very structured infrastructure and architecture

- Significantly improves Verification Efficiency

- Assures a far better Design Quality

- Recommended by Doulos for Testbench architecture

- ESA projects to extend the functionality

- IEEE Standards Association Open source project

- Included with various simulators

- Runs on GHDL

IEEE S/

# UVVM: UVM for VHDL designers

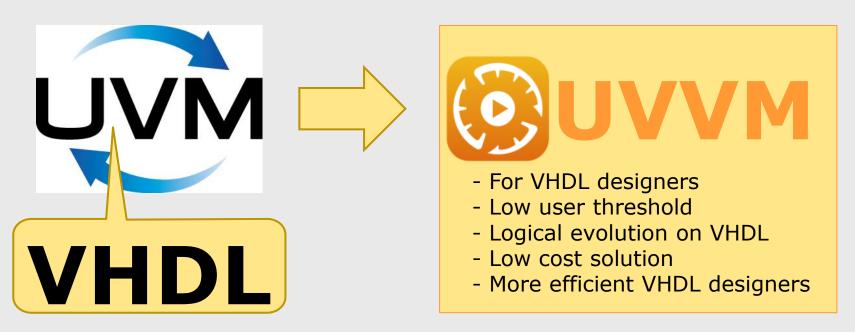

VHDL was declared as "dying" already in 2003 - and in 2007, - and ....

BUT - According to Wilson research September 2020:

## VHDL for FPGA: >50% world-wide

4

# UVVM – World-wide

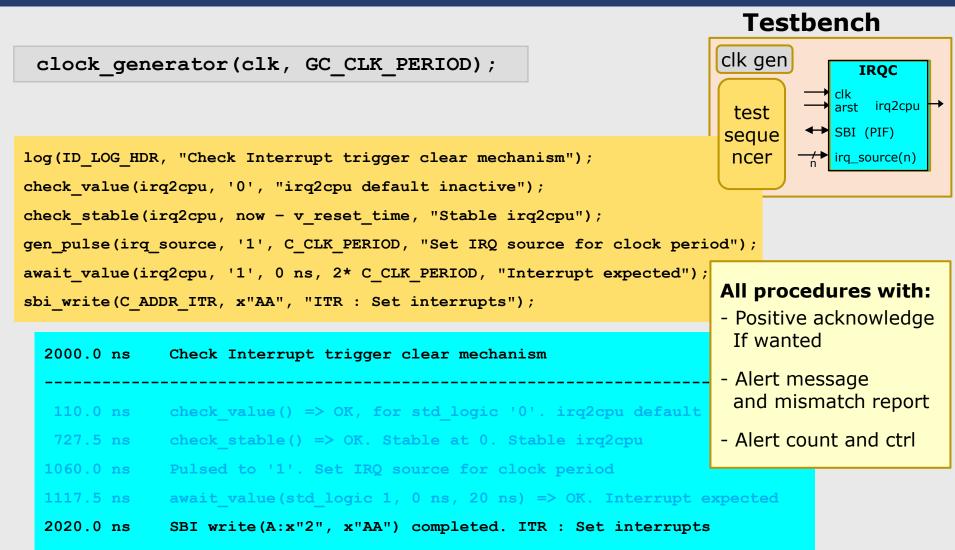

## Example on test sequencer code and transcript/log

# **UVVM Utility Library**

Testbench infrastructure library

- log(), alert(), report\_alert\_counters()

- check\_value(), await\_value()

- check\_stable(), await\_stable()

- clock\_generator(), adjustable\_clock\_generator()

- random(), randomize()

- gen\_pulse()

- block\_flag(), unblock\_flag(), await\_unblock\_flag()

- await\_barrier()

- enable\_log\_msg(), disable\_log\_msg()

- to\_string(), fill\_string(), to\_upper(), replace(), etc...

- normalize\_and\_check()

- set\_log\_file\_name(), set\_alert\_file\_name()

- wait\_until\_given\_time\_after\_rising\_edge()

- etc...

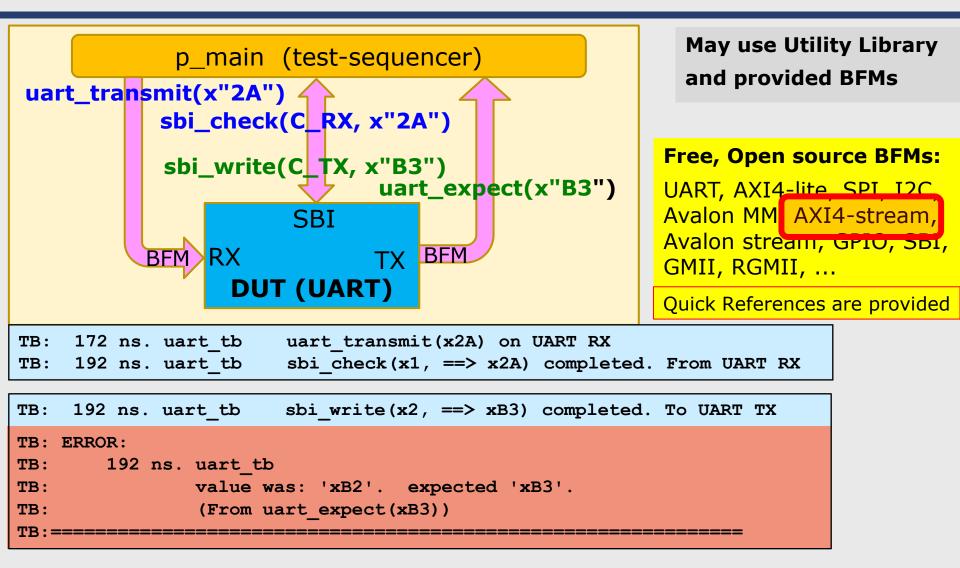

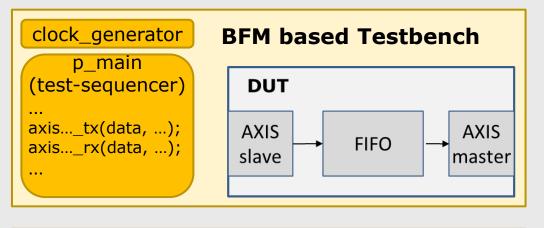

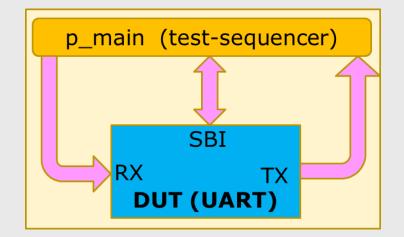

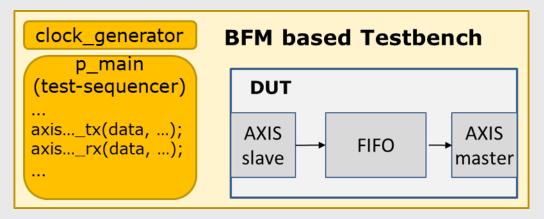

# Simple data communication

AXI-stream - BFM based TB - as simple as possible

- No test harness (for simplicity)

- Sequencer has direct access to DUT signals

- Thus BFMs from p\_main can also see the DUT signals

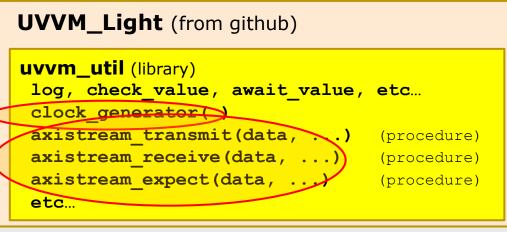

- Simplified UVVM

- For simple usage

- Subset of UVVM No VVCs or VCC support

- All BFMs in the same directory and library

Only need to download from Github (clone or zip) and compile (total 5 min)

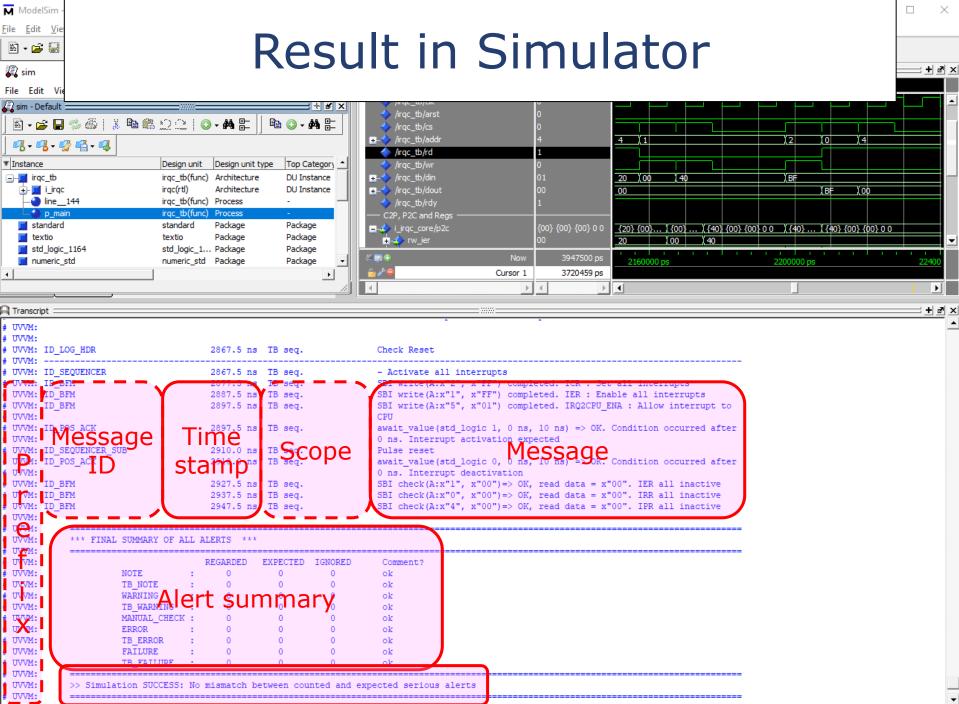

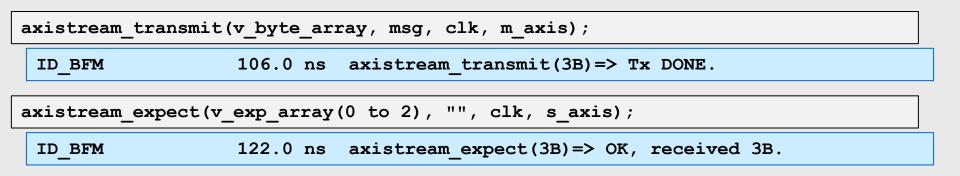

# Resulting transcript +Debug

Note: Removed Prefix and Scope to show on a single line.

## May add more info for debugging

| enable_log_msg(ID_PACK | ET_INITIATE | :); enable_log_msg(ID_PACKET_DATA);                       |

|------------------------|-------------|-----------------------------------------------------------|

| ID_PACKET_INITIATE     | 52.0 ns     | <pre>axistream_transmit(3B)=&gt;</pre>                    |

| ID_PACKET_DATA         | 52.0 ns     | <pre>axistream_transmit(3B)=&gt; Tx x"00", byte# 0.</pre> |

| ID_PACKET_DATA         | 68.0 ns     | <pre>axistream_transmit(3B)=&gt; Tx x"01", byte# 1.</pre> |

| ID_PACKET_DATA         | 82.0 ns     | <pre>axistream_transmit(3B)=&gt; Tx x"02", byte# 2.</pre> |

| ID_PACKET_COMPLETE     | 106.0 ns    | axistream_transmit(3B)=> Tx DONE.                         |

May add similar debugging info for data reception

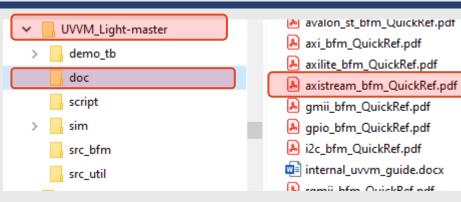

# **Documentation BFM**

Similar docs for all BFMs

# **Documentation BFM**

## **AXI4-Stream BFM** – Quick Reference

- Syntax + Overloads

- Examples

- Explanations

#### AXI4-Stream Master (see page 2 for AXI4-Stream Slave)

| axistream_transmit[_bytes] (data_array, [                                             | BFM Configuration record 't_axist                                                                                                                                                                                                                                                                                                                                                                                                     | ream_bfm_config′                                                                                                                                                                                  |                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example (tdata'length = 16) : axistream_transmit ( (x"D0"                             | Record element                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Type</b>                                                                                                                                                                                       | C_AXISTREAM_BFM_CONFIG_DEFAULT                                                                                                                                                                                              |

| Example (tdata'length = 8) : axistream_transmit ( (x"D0"                              | max_wait_cycles                                                                                                                                                                                                                                                                                                                                                                                                                       | integer                                                                                                                                                                                           | 100                                                                                                                                                                                                                         |

| Example: axistream_transmit(v_data_array(0 to v_numByt                                | max_wait_cycles_severity                                                                                                                                                                                                                                                                                                                                                                                                              | t_alert_level                                                                                                                                                                                     | ERROR                                                                                                                                                                                                                       |

| Example: axistream_transmit(v_data_array(0 to v_numByt                                | clock_period                                                                                                                                                                                                                                                                                                                                                                                                                          | time                                                                                                                                                                                              | -1 ns                                                                                                                                                                                                                       |

| Example: axistream_transmit(v_data_array(0 to v_numByt                                | clock_period_margin                                                                                                                                                                                                                                                                                                                                                                                                                   | time                                                                                                                                                                                              | 0 ns                                                                                                                                                                                                                        |

| Example: axistream_transmit(v_data_array(0 to v_numByt                                | clock_margin_severity                                                                                                                                                                                                                                                                                                                                                                                                                 | t_alert_level                                                                                                                                                                                     | TB_ERROR                                                                                                                                                                                                                    |

| Note! Use axistream_transmit_bytes () when using t_byte_                              | setup_time                                                                                                                                                                                                                                                                                                                                                                                                                            | time                                                                                                                                                                                              | -1 ns                                                                                                                                                                                                                       |

| Configuration<br>- Protocol Behaviour<br>- Compliance checking<br>- Simulation set-up | hold_time<br>hold_time<br>bfm_sync<br>match_strictness<br>byte_endianness<br>valid_low_at_word_num<br>valid_low_multiple_random_prob<br>valid_low_duration<br>valid_low_max_random_duration<br>check_packet_length<br>protocol_error_severity<br>ready_low_at_word_num<br>ready_low_multiple_random_prob<br>ready_low_duration<br>ready_low_max_random_duration<br>ready_low_max_random_duration<br>ready_default_value<br>id_for_bfm | time<br>t_bfm_sync<br>t_match_strictness<br>t_byte_endianness<br>integer<br>real<br>integer<br>boolean<br>t_alert_level<br>integer<br>real<br>integer<br>real<br>integer<br>std_logic<br>t_msg_id | -1 ns<br>SYNC_ON_CLOCK_ONLY<br>MATCH_EXACT<br>FIRST_BYTE_LEFT<br>0<br>0.5<br>0<br>5<br>false<br>ERROR<br>0<br>0.5<br>0<br>5.<br>1<br>1<br>5<br>1<br>1<br>5<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

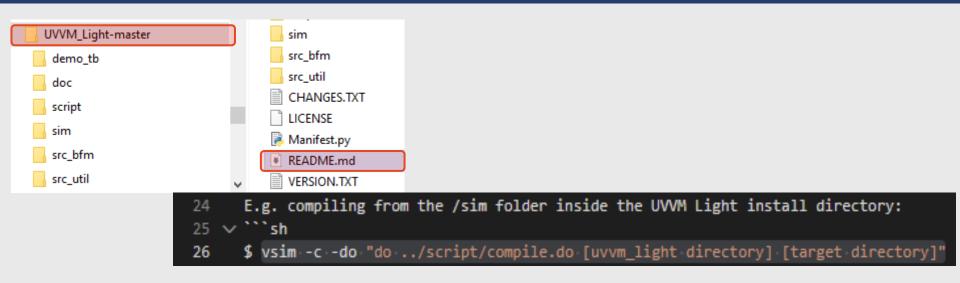

# Compiling UVVM Light

avalon\_st\_btm\_QuickKet.pdt

axi\_bfm\_QuickRef.pdf

axilite\_bfm\_QuickRef.pdf

axistream\_bfm\_QuickRef.pdf

gmii\_bfm\_QuickRef.pdf

gpio\_bfm\_QuickRef.pdf

i2c\_bfm\_QuickRef.pdf

internal\_uvvm\_guide.docx

R camii hfm OuickPaf adf

## vsim -c -do "do ../script/compile.do ../ ."

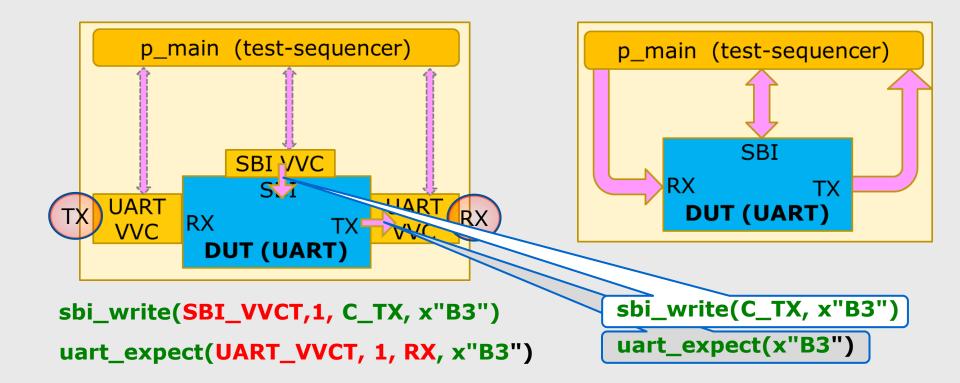

# BFM procedures are not sufficient

## BFM: Defined here as a procedure only

- BFMs are great for simple testbenches

- Dedicated procedures in a simple package

- Just reference and call from a process

- BUT

- A process can only do one thing at a time

- Either execute that BFM

- Or execute another BFM

- Or do something else

- To do more than one thing:

→ Need an entity (or component)

(VC = Verification Component)

sbi\_write(C\_TX, x"B3")

uart\_expect(x"B3")

VVC: VHDL Verification Component (UVVM VC with extended functionality)

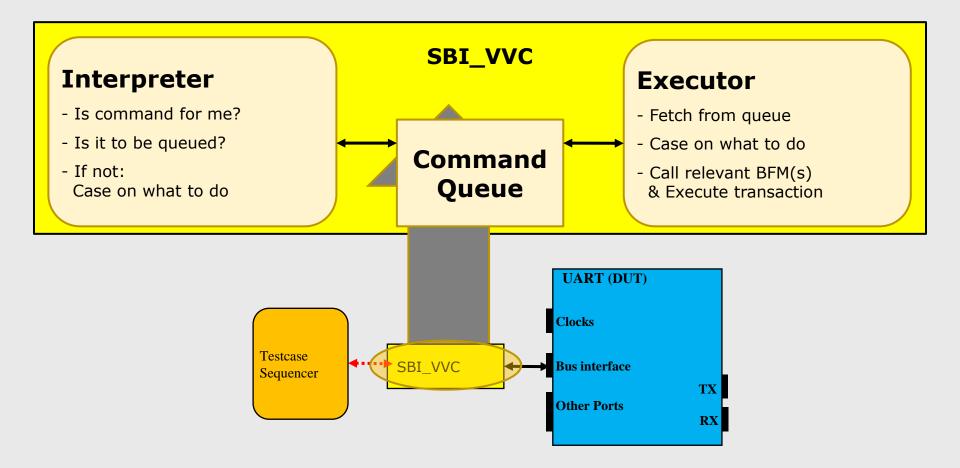

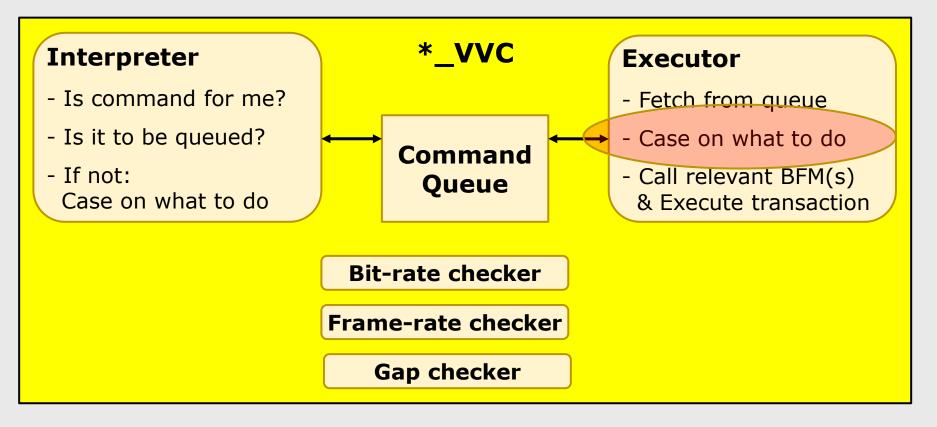

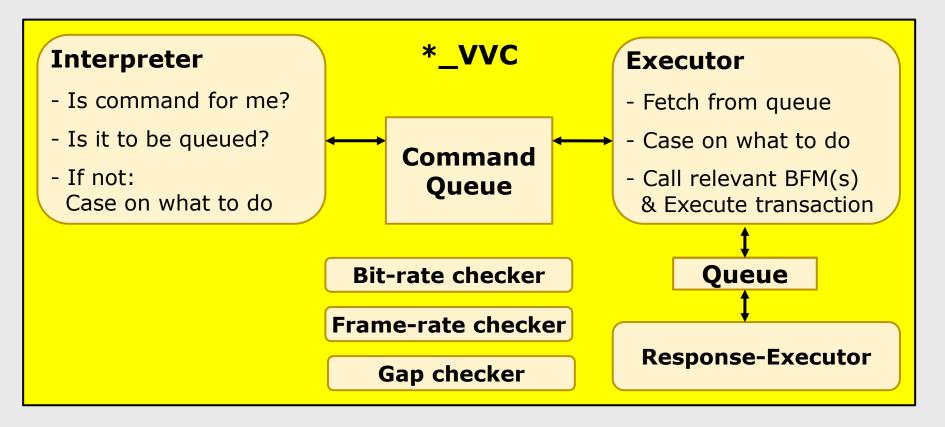

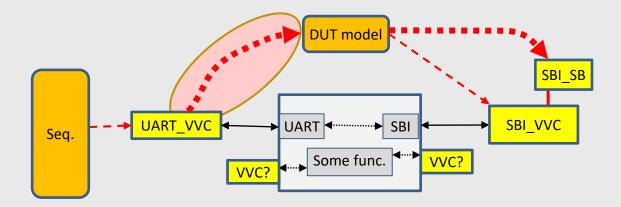

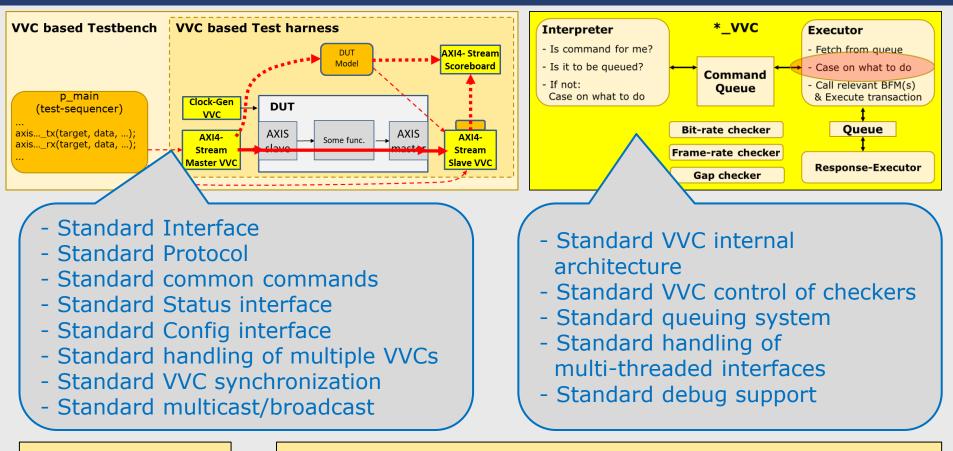

# VVC: VHDL Verification Component

# BFM to VVC: How?

### **UVVM VVCs also include:**

Delay-insertion, command queuing, completion detection, activity registration, multicast & broadcast, termination, set-up, data fetch, multi-channel support, interface checkers, scoreboards, transaction info, local sequencers, etc ...

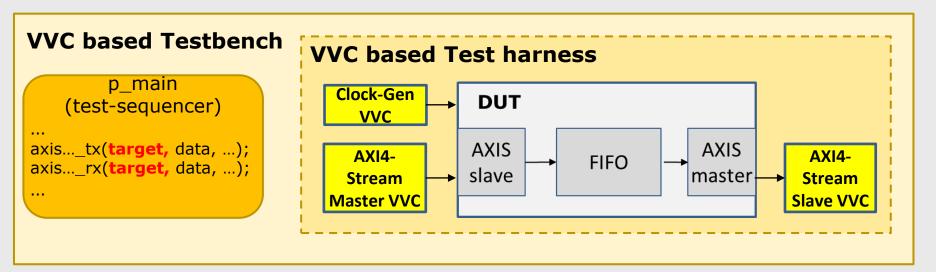

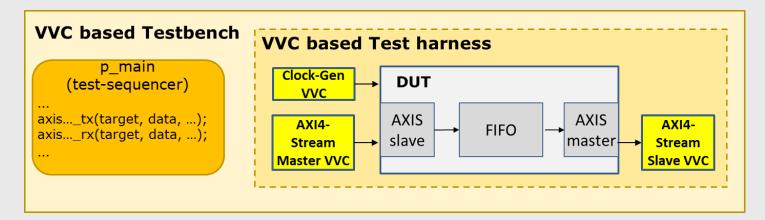

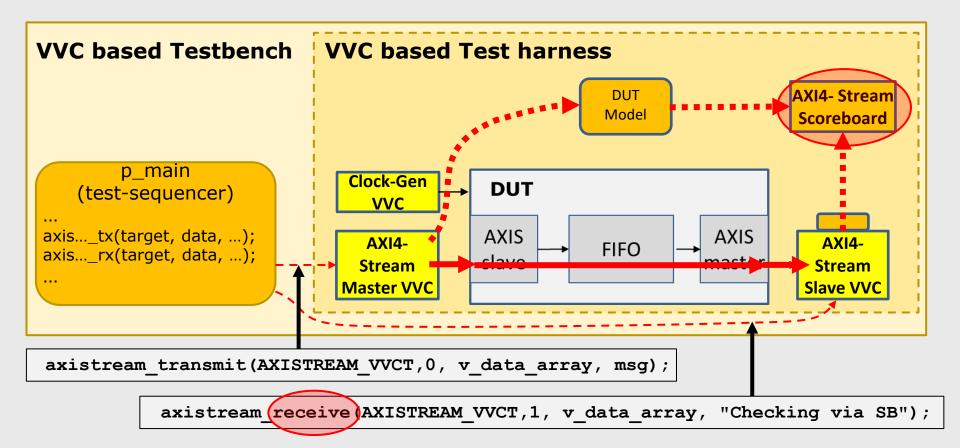

# AXI-stream - VVC based TB (1)

axistream\_transmit(target, data, ...);

axistream\_expect(target, data, ...);

# AXI-stream - VVC based TB (2)

# Resulting transcript +Debug

## Note the changing scope

| <pre>axistream_transmit(AXISTREAM_VVCT,0, v_data_array, msg);</pre>                                        |  |

|------------------------------------------------------------------------------------------------------------|--|

| ID_UVVM_SEND_CMD 50.0 ns TB seq.(uvvm)<br>->axistream_transmit(AXISTREAM_VVC,0, 512 bytes): 'TX 512B' [6]  |  |

| ID_PACKET_DATA 24202.0 ns AXISTREAM_VVC,0<br>axistream_transmit(512B)=> Tx x"ED", byte# 493. 'TX 512B' [6] |  |

| ID_PACKET_COMPLETE 24346.0 ns AXISTREAM_VVC,0<br>axistream_transmit(512B)=> Tx DONE. 'TX 512B' [6]         |  |

axistream\_expect(AXISTREAM\_VVCT,1, v\_exp\_array, "Expecting \*\*\*\* "); ID\_UVVM\_SEND\_CMD 50.0 ns TB seq.(uvvm) ->axistream\_expect\_bytes(AXISTREAM\_VVC,1, 512b): 'Expecting 512b' [7] - Plus similar additional verbosity as for Transmit - Plus for both: Debug-messages when command reaches Interpreter and Executor

# **Documentation VVC**

bitvis\_vip\_wishbone

Similar docs for all BFMs, VVCs, UVVM and other VIP

VHDL designers - An introduction

# **Documentation VVC**

#### 1 VVC procedure details

| cedure<br>stream_transmit[_bytes]()                                                          | Description                                                                                                                     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| sircani_iranshiitt_bytcsi(/                                                                  | axistream_transmit[_bytes] (VVCT, vvc_instance_idx, data_array, [user_array, [strb_array, id_array, dest_array]], msg, [scope]) |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                                                              | commands have complet<br>the AXI4-Stream BFM Q                                                                                  | procedure can only be called when the AXISTREAM VVC is instantiated - Explanations                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                                                              | Examples:                                                                                                                       |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 3 VVC Configuration                                                                          |                                                                                                                                 |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Record element                                                                               | Туре                                                                                                                            | C AXISTREAM BFM CONFIG DEFAULT                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| nter_bfm_delay                                                                               | t_inter_bfm_delay                                                                                                               | C_AXISTREAM_INTER_BFM_DELAY_DEFAULT                                                                | Delay between any requested BFM accesses towards the DUT.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| - TIME_START2START: Time from a BFM start to the nex                                         |                                                                                                                                 |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| BFM Config as 1                                                                              |                                                                                                                                 | Defaults are fine                                                                                  | (A TB_WARNING will be issued if access<br>takes longer than TIME_START2START).<br>- TIME_FINISH2START: Time from a BFM end to the next BFM start.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Additional VVC                                                                               | setup                                                                                                                           |                                                                                                    | Any insert_delay() command will add to the above minimum delays, giving for instant<br>the ability to skew the BFM starting time.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| cmd_queue_count_max                                                                          | natural                                                                                                                         | C_CMD_QUEUE_COUNT_MAX                                                                              | Maximum pending number in command queue before queue is full. Adding additional<br>commands will result in an ERROR.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| cmd_queue_count_threshold                                                                    | natural                                                                                                                         | C_CMD_QUEUE_COUNT_THRESHOLD                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                                                              |                                                                                                                                 |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| cmd_queue_count_threshold_severity                                                           | t_alert_level                                                                                                                   | C_CMD_QUEUE_COUNT_THRESHOLD_SEVERITY                                                               | queue exceeds this count. Used for early warning if command queue is almost full. V                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                                                                              | t_alert_level<br>natural                                                                                                        |                                                                                                    | queue exceeds this count. Used for early warning if command queue is almost full. W<br>be ignored if set to 0.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| cmd_queue_count_threshold_severity                                                           |                                                                                                                                 | C_CMD_QUEUE_COUNT_THRESHOLD_SEVERITY                                                               | Severity of alert to be initiated if exceeding cmd_queue_count_threshold                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| cmd_queue_count_threshold_severity<br>result_queue_count_max                                 | natural<br>natural                                                                                                              | C_CMD_QUEUE_COUNT_THRESHOLD_SEVERITY<br>C_RESULT_QUEUE_COUNT_MAX                                   | queue exceeds this count. Used for early warning if command queue is almost full. We ignored if set to 0.         Severity of alert to be initiated if exceeding cmd_queue_count_threshold         Maximum number of unfetched results before result_queue is full.         An alert with severity 'result_queue_count_threshold_severity' will be issued if result queue exceeds this count. Used for early warning if result queue is almost full. Will be                      |  |  |  |  |  |

| cmd_queue_count_threshold_severity<br>result_queue_count_max<br>result_queue_count_threshold | natural<br>natural                                                                                                              | C_CMD_QUEUE_COUNT_THRESHOLD_SEVERITY<br>C_RESULT_QUEUE_COUNT_MAX<br>C_RESULT_QUEUE_COUNT_THRESHOLD | queue exceeds this count. Used for early warning if command queue is almost full. We ignored if set to 0.         Severity of alert to be initiated if exceeding cmd_queue_count_threshold         Maximum number of unfetched results before result_queue is full.         An alert with severity 'result_queue_count_threshold_severity' will be issued if result queue exceeds this count. Used for early warning if result queue is almost full. Will be ignored if set to 0. |  |  |  |  |  |

The configuration record can be accessed from the Central Testbench Sequencer through the shared variable array, e.g.:

shared\_axistream\_vvc\_config(1).inter\_bfm\_delay.delay\_in\_time := 50 ns; shared\_axistream\_vvc\_config(1).bfm\_config.clock\_period := 10 ns;

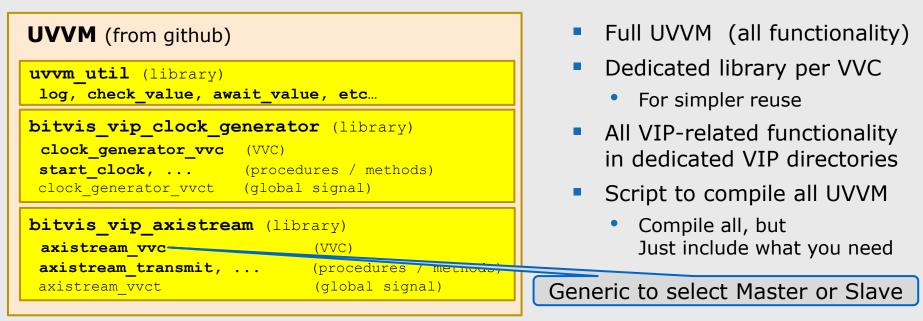

# Compiling UVVM

| 100/04                                   |                                                                                 |

|------------------------------------------|---------------------------------------------------------------------------------|

| ✓ UVVM-master                            | bitvis_vip_gpio                                                                 |

| supplementary_doc                        | bitvis_vip_hvvc_to_vvc_bridge                                                   |

| > bitvis_irqc                            | bitvis_vip_i2c                                                                  |

| > bitvis_uart                            | bitvis_vip_rgmii                                                                |

| > bitvis_vip_avalon_mm                   | bitvis_vip_sbi                                                                  |

| > bitvis_vip_avalon_st                   | bitvis_vip_scoreboard                                                           |

| > bitvis_vip_axi                         | bitvis_vip_spec_cov                                                             |

|                                          | bitvis_vip_spi                                                                  |

| > bitvis_vip_axilite                     | bitvis_vip_uart                                                                 |

| > bitvis_vip_axistream                   | bitvis_vip_wishbone \script> vsim -c -do "compile all.do"                       |

| bitvis_vip_clock_generato                |                                                                                 |

| > bitvis_vip_error_injection             | uvvm_util                                                                       |

| > bitvis_vip_ethernet                    | uvvm_vvc_framework                                                              |

| > onvis_vip_ememer                       | CHANGES.TXT                                                                     |

| > bitvis_vip_gmii                        | FAQ.txt                                                                         |

| bitvis_vip_gpio                          | GETTING_STARTED.md                                                              |

| > bitvis_vip_hvvc_to_vvc_br              |                                                                                 |

| 60                                       | The easiest way to compile the complete UVVM with everything (Utility Library,  |

| > bitvis_vip_i2c                         | VVC Framework, BFMS, VVCs, etc.) is to go to the top-level script directory and |

| 1. • • • • • • • • • • • • • • • • • • • |                                                                                 |

|                                          | run 'compile_all.do' inside Modelsim/Questasim/RivieraPro/ActiveHDL.            |

# VVC: Easy to extend

# Easy to add local sequencers Easy to add checkers/monitors/etc

# VVC: Easy to extend

- Easy to handle split transactions

- Easy to handle out of order execution

# VVC Advantages

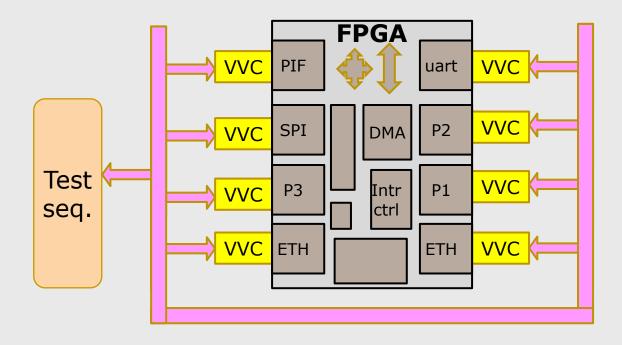

- Simultaneous activity on multiple interfaces

- Encapsulated  $\rightarrow$  Reuse at all levels

- Queue  $\rightarrow$  May initiate multiple high level commands

- Local Sequencers for predefined higher level commands

## Only in UVVM VVCs:

- UNIQUE: Control all VVCs from a single sequencer!

- May insert delay between commands from sequencer

→ The only system to target cycle related corner cases

- Simple handling of split transactions and out of order protocols

- Common commands to control VVC behaviour

- Simple synchronization of interface actions from sequencer

- May use Broadcast and Multicast

## Better Overview, Maintenance, Extensibility and Reuse

# Keeping the overview

- May use any number of VVCs

- May use any number of instances of each VVC type

- May control them all simultaneously and also control command delays

- May control all from a single test sequencer (or two or more)

- Get total overview by looking at one file of sequential commands only

# Lot's of free UVVM BFMs and VVCs

- AXI4-lite

- AXI4 Full

- AXI-Stream Transmit and Receive

- UART Transmit and Receive

- SBI

- SPI Transmit and Receive

- I2C Transmit and Receive

- GPIO

- Avalon MM

- Avalon Stream Transmit and Receive

- RGMII Transmit and Receive

- GMII Transmit and Receive

- Ethernet Transmit and Receive

- Wishbone

- Clock Generator

- Error Injector

## All:

- Free

- Open Source

- Well documented

- Example Testbenches

The largest collection of **VHDL Interface Models**

### **VVC: VHDL Verif. Comps.**

- Includes the corresponding BFM Allows:

- Simultaneous interface handling

- Synchronization of interfaces

- Skewing between interfaces

- Additional protocol checkers

- Local sequencers

- Activity detection

- Simple reuse between projects

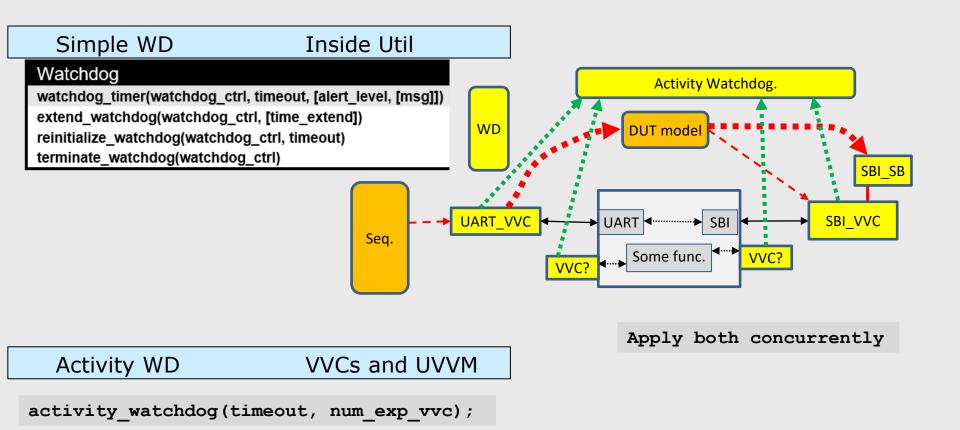

# Added 2019-20 – in cooperation with ESA

- ESA Extensions in ESA-UVVM-1

- Scoreboards

- Monitors

- Controlling randomisation and functional coverage

- Error injection (Brute force and Protocol aware)

- Local sequencers

- Controlling property checkers

- Watchdog (Simple and Activity based)

- Transaction info

- Hierarchical VVCs And Scoreboards for these

- **Specification Coverage** (Requirement/test coverage)

ESA is helping VHDL designers speed up FPGA and ASIC development and improve their product quality!

# Transaction info transfer

Transaction info Inside VVC All UVVM VVCs

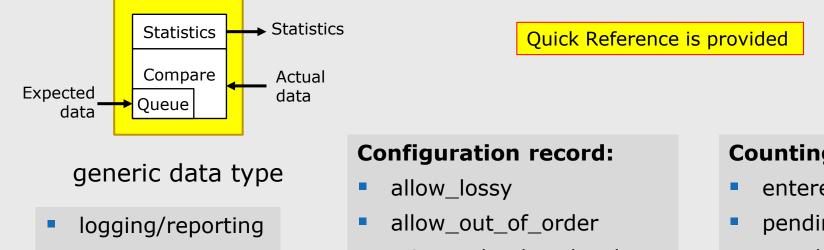

# Generic Scoreboard

flushing queue

clearing statistics

insert, delete, fetch

ignore\_initial\_mismatch

- mismatch\_alert\_level

- etc...

## **Counting:**

- entered

- pending

- matched

- mismatched

- dropped

- deleted

- initial garbage

- indexed on either entry or position

- optional source element (in addition to expected + actual)

31 UVVM: UVM for VHDL designers - An introduction

# Watchdogs

- Assure that all requirements have been verified

- **1**.Specify all requirements

| Requirement Label | Description                         |

|-------------------|-------------------------------------|

| MOTOR_R1          | The acceleration shall be ***       |

| MOTOR_R2          | The top speed shall be given by *** |

| MOTOR_R3          | The deceleration shall be ***       |

| MOTOR_R4          | The final position shall be ***     |

2.Report coverage from test sequencer (or other TB parts)3.Generate summary report

- Solutions exist to report that a testcase finished successfully

- BUT reporting that a testcase has finished is not sufficient

## Specification Coverage (2)

etc..

What if multiple requirements are covered by the same testcase?

| <b>Requirement Label</b> | Description                         |

|--------------------------|-------------------------------------|

| MOTOR_R1                 | The acceleration shall be ***       |

| MOTOR_R2                 | The top speed shall be given by *** |

| MOTOR_R3                 | The deceleration shall be ***       |

| MOTOR_R4                 | The final position shall be ***     |

• E.g. Moving/turning something to a to a given position R1: Acceleration R2: Speed R3: Deceleration 4: Position

- Generates various types of reports

- Coverage per requirement

- Test cases covering each requirement

- Requirements covered by each Test case

- Accumulated over multiple Test cases

# The new stuff – October 2021

- Enhanced Randomisation

- Advanced randomisation in a simple way

- Optimised Randomisation

- Randomisation without replacement

- Weighted according to target distribution AND previous events

- $\rightarrow$  the lowest number of randomisations for a given target

- Functional Coverage

- Based on functional coverage in SV

- But in VHDL, and without all the complexity of SV and UVM

- Fully integrated with UVVM, but may be used stand-alone

# Quality Well integrated with UVVM

UVVM Enhanced Randomisation

- Alert handling and logging in particular

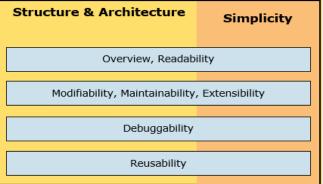

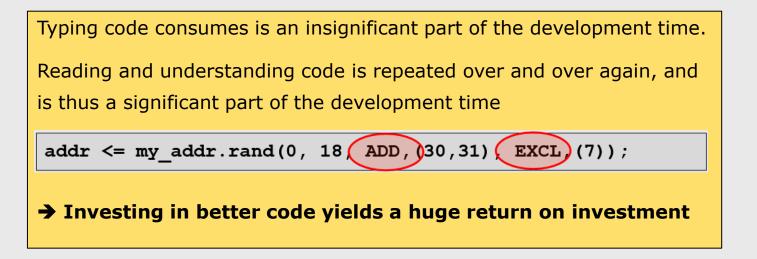

- Strong focus on Overview & Readability

- Adding keywords to ease understanding

- Easy to Maintain and Extend

# Single Method approach

## "Standard" approach: Randomisation in one single command

Simple randomisation is always easy to understand

addr <= my\_addr.rand(0, 18);</pre>

More complex randomisation is normally more difficult to understand BUT – there are ways to significantly improve this

Similar readability focus for weighting

addr <= my\_addr.rand\_val\_weight((0,2),(1,3),(2,5));

addr <= my\_addr.rand\_range\_weight((0,18,4),(19,31,1));

38 UVVM: UVM for VHDL designers - An introduction EmLogic</pre>

# Multi-method approach (1)

- Extends the functionality of the single method approach

- Single method approach:

```

addr_1 <= my_addr.rand(0, 18, ADD,(30,31), EXCL,(7));

addr_2 <= my_addr.rand(0, 18, ADD,(30,31), EXCL,(7));</pre>

```

• Multi-method - equivalent

```

my_addr.add_range(0, 18);

my_addr.add_val((30,31));

my_addr.excl_val((7));

addr_1 <= my_addr.randm(VOID);

addr_2 <= my_addr.randm(VOID);</pre>

```

Note: rand**m**() (For clarity and to avoid any ambiguity)

Allows adding more ranges, sets or exclusions

```

my_addr.add_range(48,63);

my_addr.add_range(80,127);

```

Allows simple inclusion of future extensions

# Functional Coverage – Typical Sequence

2-254

Define a variable of type t\_coverpoint

variable cp\_payload\_size : t\_coverpoint;

Add the bins

```

cp_payload_size.add_bins(bin(0));

cp_payload_size.add_bins(bin(1));

cp_payload_size.add_bins(bin_range(2,254,1));

cp_payload_size.add_bins(bin(255,256,2));

```

Tick off bins as their corresponding payload size is used

cp\_payload\_size.sample\_coverage(payload\_size);

Continue sending packets until coverage target is reached

while not cp\_payload\_size.coverage\_completed(VOID);

### **UVVM** also has transition coverage

# Some reports – out of many

| # UVVI | м:  |                              |              |                                       |               |            |                |                     |    |

|--------|-----|------------------------------|--------------|---------------------------------------|---------------|------------|----------------|---------------------|----|

| # UVVI | M:  | 0 ns *** COVERAGE SUMMARY RE | PORT (NON VE | RBOSE): TB seq                        | . ***         |            |                |                     |    |

| # UVVI | М:  |                              |              |                                       |               |            |                |                     |    |

| # UVVI | мĆ  | Coverpoint: Cov              | pt_1         |                                       |               |            |                |                     |    |

| # UVVI | М:  | Coverage (for goal 100). Bin | IS: 60.00%,  | Hits: 76.47%                          |               |            |                |                     |    |

| # UVVI | М:  |                              |              |                                       |               |            |                |                     |    |

| # UVVI | М:  | BINS                         | HITS         | MIN HITS                              | HIT COVERAGE  | NA         | ME             | ILLEGAL/IGNORE      |    |

| # UVVI | М:  | (256 to 511)                 | 1            | N/A                                   | N/A           | illega     | l_addr         | ILLEGAL             |    |

| # UVVI | М:  | (0 to 125)                   | 6            | 8                                     | 75.00%        | mem_ad     | dr_low         | -                   |    |

| # UVVI | М:  | (126, 127, 128)              | 3            | 1                                     | 100.00%       | mem_ad     | dr_mid         | -                   |    |

| # UVVI | М:  | (129 to 255)                 | 14           | 4                                     | 100.00%       | mem_ad     | dr_high        | -                   |    |

| # UVVI | М:  | (0->1->2->3)                 | 0            | 2                                     | 0.00%         | transi     | tion_1         | -                   |    |

| # UVVI | М:  | transition_2                 | 2            | 2                                     | 100.00%       | transi     | tion_2         | -                   |    |

| # UVVI | М:  |                              |              |                                       |               |            |                |                     |    |

| # UVVI | М:  | transition_2: (0->15->127->2 | 48->249->250 | ->251->252->25                        | 3->254)       |            |                |                     |    |

| # UVVI | М:  |                              |              |                                       |               |            |                |                     |    |

|        | # 1 | UVVM: ======                 |              |                                       |               |            |                |                     |    |

|        |     | UVVM: 0 ns ** OVERALL COVER  | AGE REPORT   | VERBOSE): TB se                       | a. ***        |            |                |                     |    |

|        |     | UVVM: Coverage (for goal 100 |              | · · · · · · · · · · · · · · · · · · · | 73.68%, Hits: | : 76.00%   |                |                     |    |

|        |     | UVVM: ======                 |              |                                       |               |            |                |                     | == |

|        | # ( | UVVM: COVERPOINT COVE        | RAGE WEIGHT  | COVERED BINS                          | COVERAGE(BIN  | NS HITS) G | OAL(BINS HITS) | % OF GOAL(BINS HITS | )  |

|        | # ( | UVVM: Covpt_1                | 1            | 3 / 5                                 | 60.00%        |            | 50%   100%     | 100.00%   76.47%    | ·  |

|        | # ( | UVVM: Covpt_2                | 1            | 3/3                                   | 100.00% 1     | 100.00%    | 100%   100%    | 100.00%   100.00%   | ŝ  |

|        | # ( | UVVM: Covpt_3                | 1            | 6/6                                   | 100.00%   1   | 100.00%    | 100%   100%    | 100.00%   100.00%   | 5  |

|        | # ( | UVVM: Covpt_4                | 1            | 0/4                                   | 0.00% 0       | 0.00%      | 100%   100%    | 0.00%   0.00%       |    |

|        | # ( | UVVM: Covpt_5                | 1            | 0 / 1                                 | 0.00%   0     | 0.00%      | 100%   100%    | 0.00%   0.00%       |    |

|        | # ( | UVVM: Covpt_6                | 1            | 4 / 4                                 | 100.00%   1   | 100.00%    | 100%   100%    | 100.00%   100.00%   | i  |

|        | # ( | UVVM: Covpt_7                | 1            | 0/3                                   | 0.00%   0     | 0.00%      | 100%   100%    | 0.00%   0.00%       |    |

|        | # ( | UVVM: Covpt_8                | 1            | 12 / 12                               | 100.00%   1   | 100.00%    | 100%   100%    | 100.00%   100.00%   |    |

|        | # ( | UVVM:                        |              |                                       |               |            |                |                     | == |

|        |     |                              |              |                                       |               |            |                |                     |    |

41

UVVM: UVM for VHDL designers - An introduction

# Pick and choose – No lock

Pick **any** Utility Library functionality: (from these plus more)

|                              | log()                |              | alert() erro |                           | error()     | <pre>manual_check()</pre> |                  |         |

|------------------------------|----------------------|--------------|--------------|---------------------------|-------------|---------------------------|------------------|---------|

|                              | check_va             | value()      |              | <pre>check_stable()</pre> |             | <pre>await_stable()</pre> |                  |         |

| await_change()               |                      |              | await_       | await_value() check_v     |             | check_va                  | value_in_range() |         |

| random() rando               |                      | omize() repo |              | port_***                  | ort_***() e |                           | _msg()           |         |

|                              | justify() fill_strin |              | ring()       | ng() to_upper() replace   |             | replace()                 | ,                |         |

| <pre>clock_generator()</pre> |                      |              |              | await_u                   | nblock_f    | lag()                     | await_ba         | rrier() |

Pick any BFM - or any VVC – or any combination

| IXA             | 4-lite | GPIO | SBI       | :     | SPI         | UART     | 12C       |

|-----------------|--------|------|-----------|-------|-------------|----------|-----------|

|                 | AXI    | AVAL | AVALON MM |       | AXI4-stream |          | on-stream |

| CLOCK_GENERATOR |        | GM   | II        | RGMII | :           | Ethernet |           |

- Pick any FIFO, Queue, Scoreboard

- Pick any Advanced Randomisation and/or Functional Coverage

- Pick Specification coverage / Requirements tracking

# Standardized? - In what way?

Simplification

VVCs from different users will work together

Users know how VVCs behave and how any test harness will work

## UVVM vs UVM

- UVVM: VHDL (2008) vs UVM: SystemVerilog

- UVVM: Component oriented

vs UVM: Object oriented

- Block diagrams are similar, but different naming and structure

- UVM is far more comprehensive and complex than UVVM

- But UVVM is sufficient for almost all testbenches

- UVVM user threshold is a fraction of the UVM threshold for VHDL users

- UVVM is just a step-by-step evolution on VHDL

- UVVM allows a gentle introduction to modern verification

- **May** be used as a first step to UVM for those who evaluate that

- Is however sufficient in itself for almost all FPGA designs

- UVVM can run on any VHDL 2008 compatible simulator

# Courses

## FPGA (and ASIC) Verification: 'Advanced VHDL Verification – Made simple'

FPGA (and ASIC) Design:

## 'Accellerating FPGA and Digital ASIC Design'

#### Design

- Design Architecture & Structure

- Clock Domain Crossing

- Coding and General Digital Design

- Reuse and Design for Reuse

- Timing Closure

- Quality Assurance at the right level

- Faster and safer design

### Verification

- Verification Architecture & Structure

- Self checking testbenches

- BFMs How to use and make

- Checking values, time aspects, etc

- Verification components

- Advanced Verif: Scoreboard, Models, etc

- State-of-the-art verification methodology

Next courses in Germany October and November. More courses on demand: On-site, Online, Public, or Hybrid

https://emlogic.no/courses/

# UVVM in a nutshell

Huge improvement potential for more structured FPGA verification