## Automating Verification Checks Synthesizing Self-Checking Test Content

David Kelf

DVClub Europe October 2022

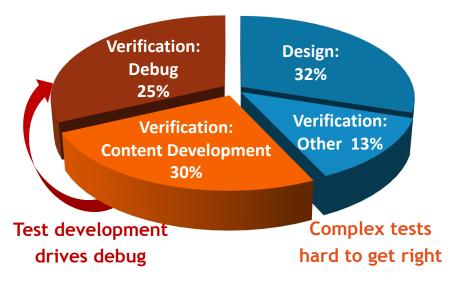

## **Explosive Verification Cost**

#### **Project Resource Deployment**

Source: Wilson Research 2020

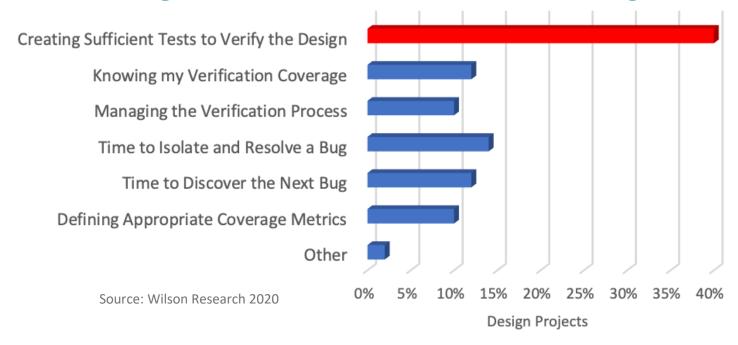

#### **Largest Functional Verification Challenge**

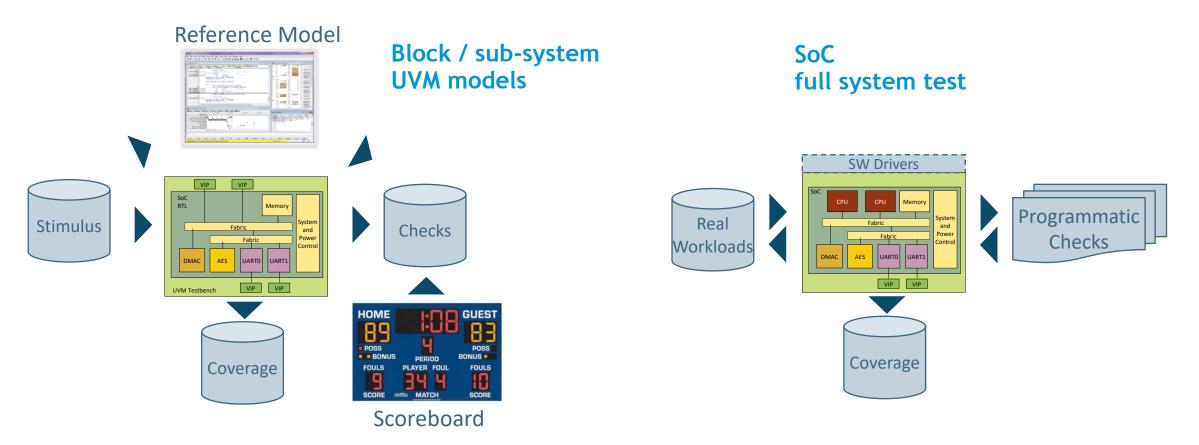

## **UVM & SoC Verification Check Alternatives Today**

Composing checks (and coverage models) can be onerous and error prone

## Formal Approach

- Traditional dynamic test method:

Send stimulus, write expected results, check coverage of test

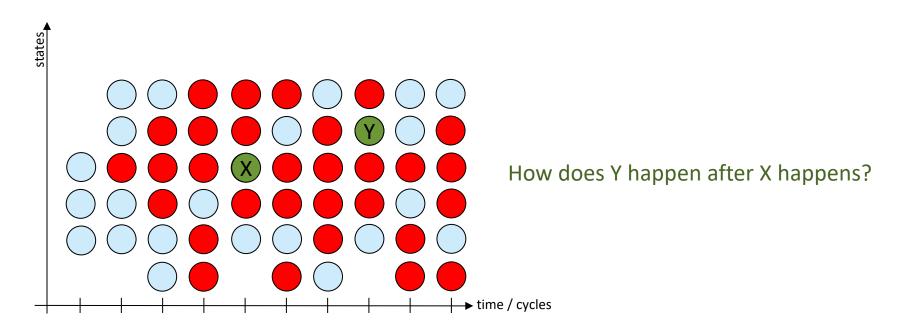

- How do Formal Verification tools approach this?

Propose check and see if it can happen based on entire state space

- Can we do the same in dynamic verification?

#### Start with the end in mind

## Synthesis approach to generate test content?

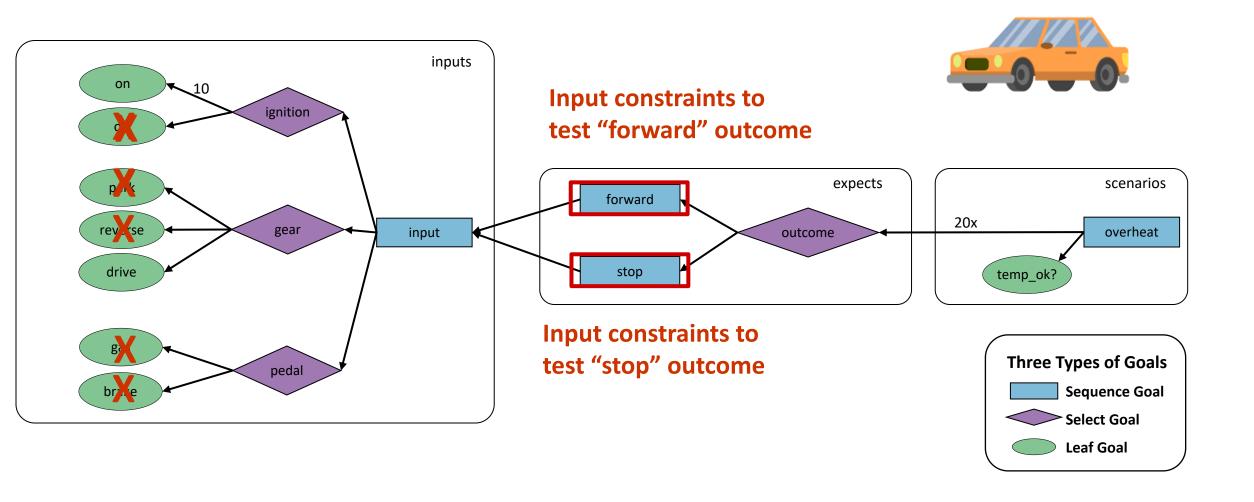

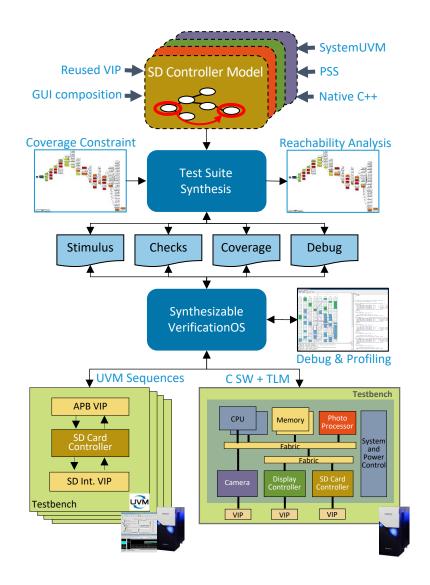

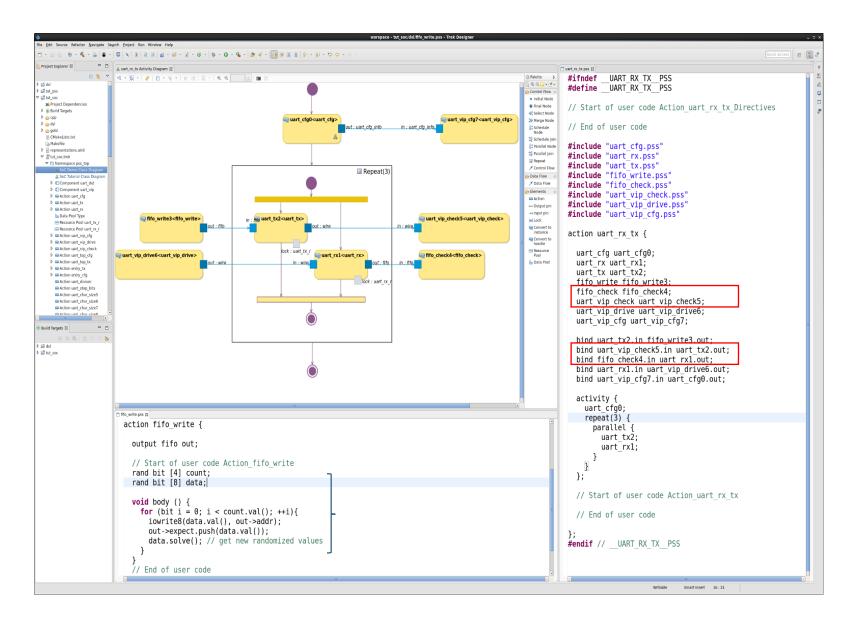

- Create a specification scenario model that shows how the device is supposed to work

- Could be composed in PSS, C++, graphically, or using SystemVIP

- Synthesize model based on coverage constraints

- Set coverage up front

- Generate entire test content automatically

- Stimulus, checks, coverage models, debug detail

- Map to verification phase and execution platform

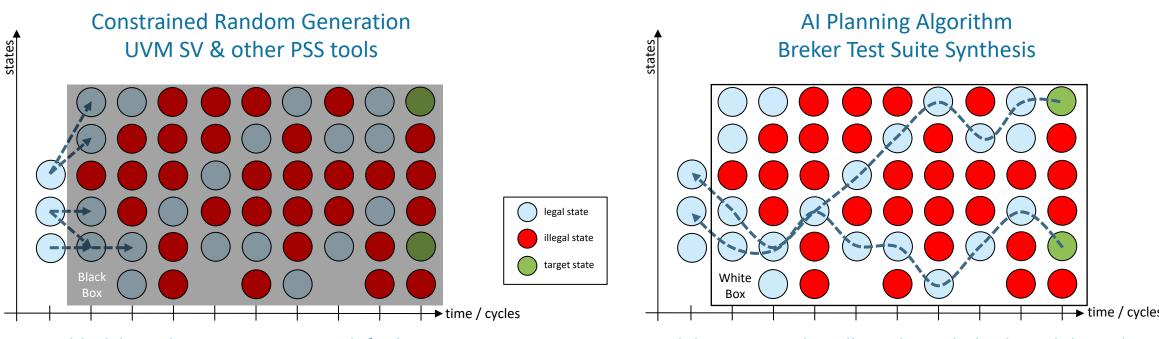

## Constrained Random vs Al Planning Algorithm Synthesis

Design black box, shotgun tests to search for key state

Low probability of finding complex bug

Starts with key state and intelligently works backward through space Deep sequential, optimized test discovers complex corner-cases

White Paper Discussing AI Planning Algorithm Test Generation on Breker Website

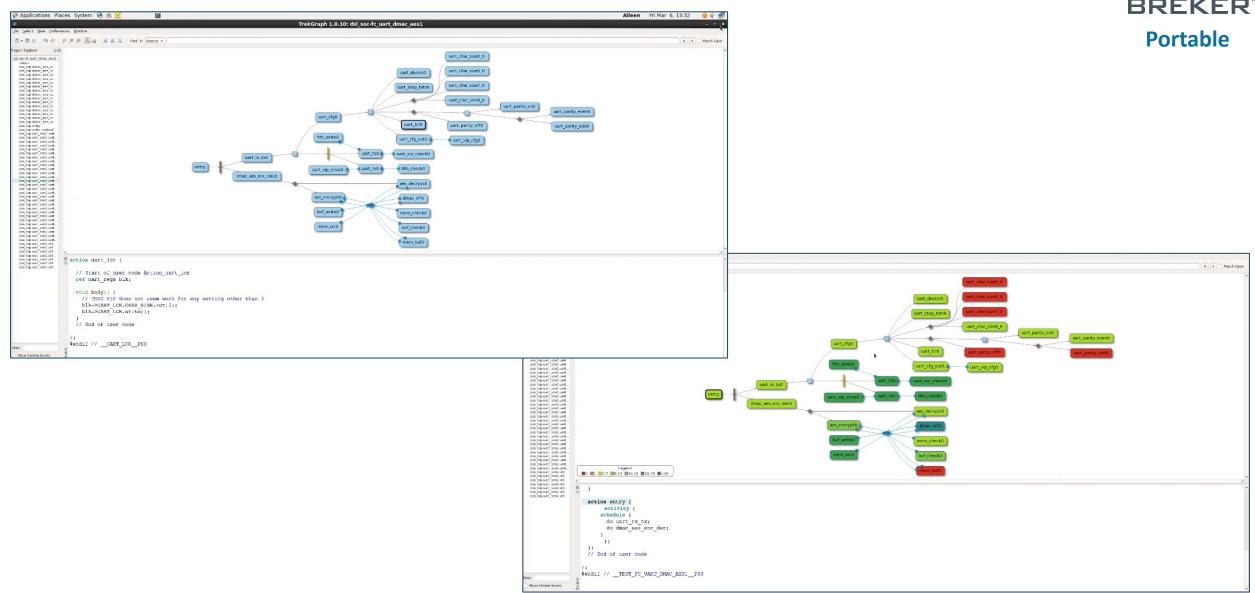

#### Block level embedded checks

## **Path Coverage Analysis**

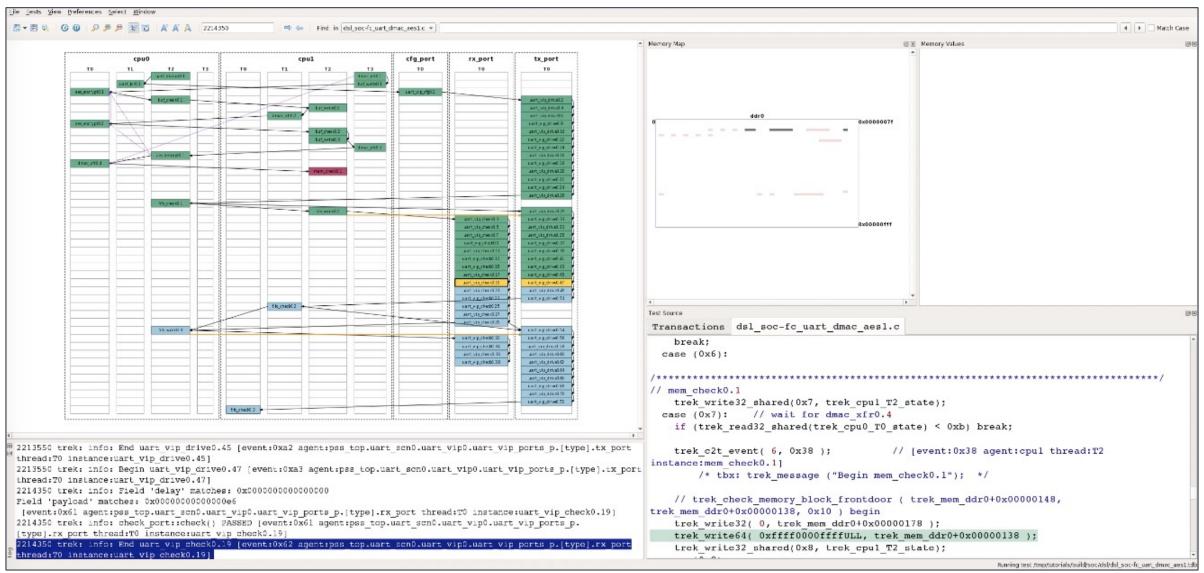

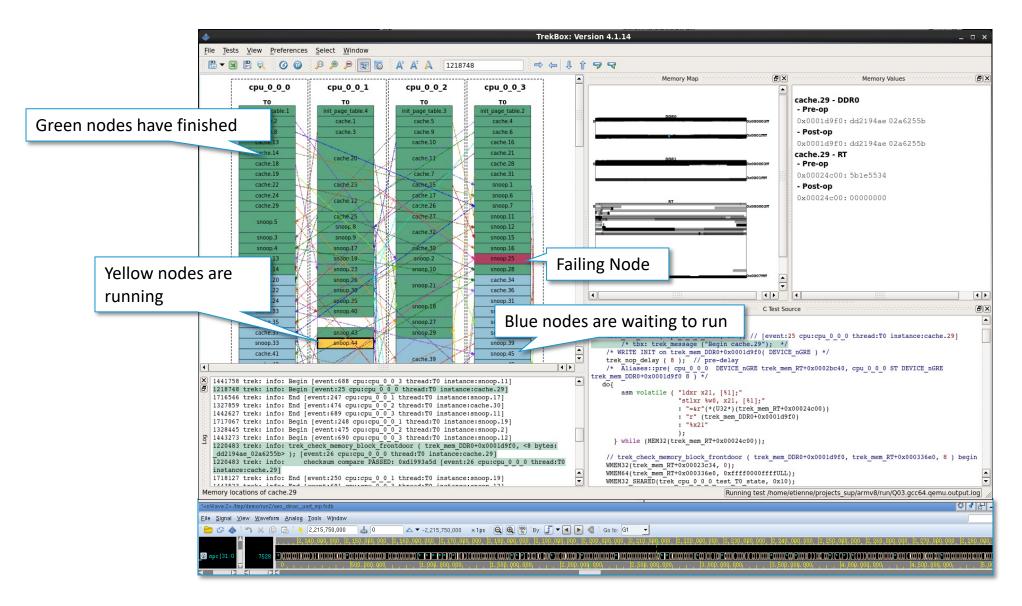

## **Self-Checking Test Execution**

#### **SoC Test Content**

## High-level Test Debug Driving Issue Resolution

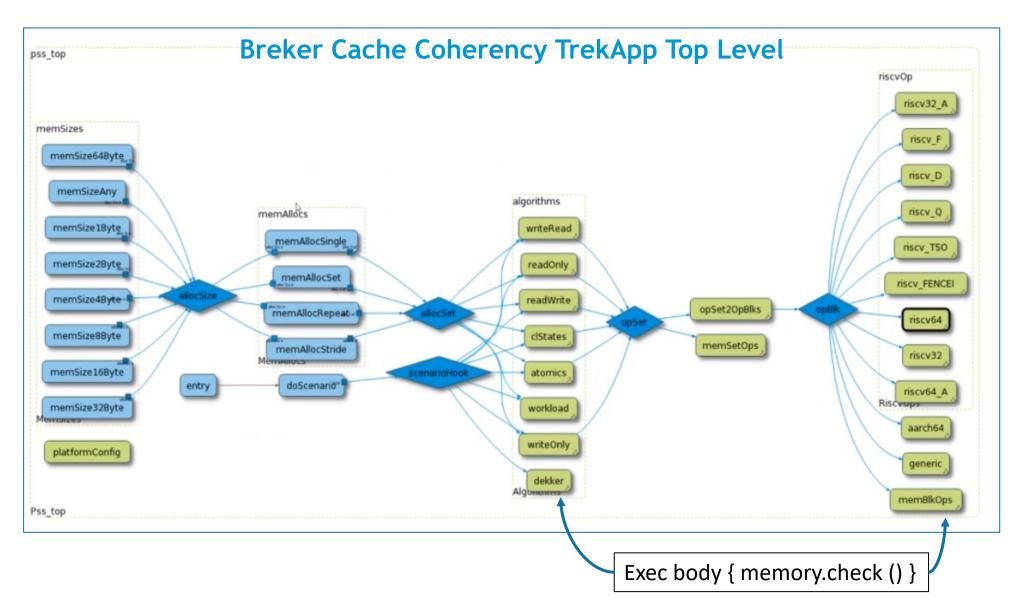

## Breker TrekApp SystemVIP Library

#### The Breker Configurable TrekApp Library

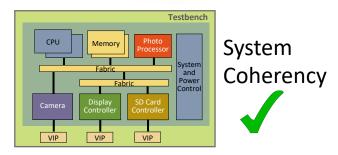

- The Cache Coherency TrekApp 2.0 verifies cache and system-level coherency in a multiprocessor SoC

- The ARM TrekApp automated integration testing of ARM based systems

- The RISC-V TrekApp handles typical processor integration issues for the RISC-V open ISA

- The Power Management TrekApp automates power domain switching verification

- The Security TrekApp automates testing of hardware access rules for HRoT fabrics

- The Networking TrekApp automates packet generation, dissection and prediction

#### **Breker: Your Verification GPS**

- Effective test content composition is the toughest verification challenge and checks/coverage is one of the most onerous activities

- Checks and coverage models may be automated via test suite synthesis leveraging an abstract executable specification

- Test Suite Synthesis automation for both UVM and SoC verification has been proven to save 5X resources while increasing coverage significantly

For more Information:

www.brekersystems.com

# Thanks for Listening! Any Questions?

brekersystems.com/resources/case-studies