# Faster TB Development with Automated Code Checks

### **CONFIDENTIAL INFORMATION**

The information contained in this presentation is the confidential and proprietary information of Synopsys. You are not permitted to disseminate or use any of the information provided to you in this presentation outside of Synopsys without prior written authorization.

### **IMPORTANT NOTICE**

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

### Introduction

- Efficiency is crucial when working with SystemVerilog UVM Testbenches. Syntax mistakes, coding violations, and the resulting problems increase the daily stress of engineers.

- Every time an engineer submits a compile after coding a part of TB, it is extremely likely for the code to fail at compile or run time due to syntactical or structural errors Needs iterative compile and simulation to fix.

- That time is measurable

- Engineers would rather have the problems:

- in their editor

- annotated with exactly the right error message to fix

- be given quick feedback if their fix worked

### What Do We Need During Code Development?

### Automated Code Checks On-the-fly Rule Checking

#### Avoid Testbench errors

- Testbench linting with elaboration and advanced analysis

- Find bugs in testbench and uncover RTL errors hidden by erroneous testbench code

### Prevent late-stage Design-under-Test (DUT) bugs and assure code quality

- Design rule checking as you type

- Assure high quality code by finding bugs early before it becomes risky to modify code

#### Improve productivity

- Integrated Development Environment

- Coding acceleration, code viewing and navigation, integration with version control, bug tracking, task management

#### Easily adopt coding styles and project methodology

- Verify legal syntax/semantics, naming conventions, unified project indentation and code formatting

- Custom rules for methodology enforcement

## On-the-fly SVTB/UVM checking

On-the-fly DUT checking

Integrated Development Environment (IDE)

**Synopsys**°

### **Testbench Checks**

- Procedural code analysis

- Dead code detection

- Time-0 problems detections, such as out-ofbounds accesses, 'unique' case violations, etc.

- 'null' class / virtual interface access

- Dynamic casting violations

- Infinite loops & recursions

- UVM specific rules

- Non-compliant or incorrect code

- Migration to UVM 1.2 or IEEE standard

- Method overrides & implementation inconsistencies or irregularities

- SVA checks

- Class constraint checks

- Data type mismatches

- In method argument, including DPI

- In assignments

- In expressions in any context

- Simulation performance rules

- Custom methodology rules

### **Design Checks**

- Synthesis results

- Combinational loops, latches, ungated flops, etc.

- Clock & reset related rules

- Drives / loads violations

- Per Index, leveraging time-0 information

- Undriven, unread

- Multiple drives, multiple driving procedures

- Interface & modport violations

- Procedural code analysis

- Dead code detection

- Time-0 problems detections, such as out-ofbounds accesses, 'unique' case violations, etc.

- Width mismatches and other data type mismatches

- Parameterized information

- Simulation performance rules

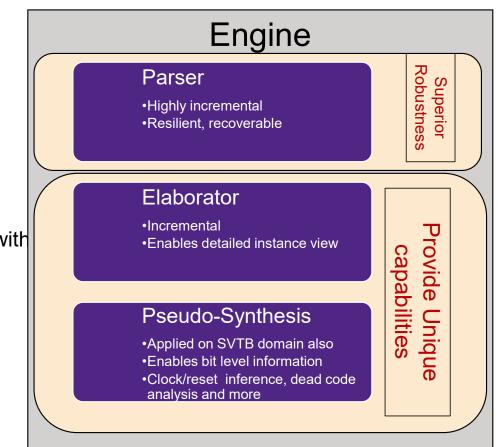

### Euclide

Technology Highlights

- Powerful EDA Engine

- Engine Differentiation:

- High performance

- Resilient and recoverable

- Robust feedback even on incomplete code or code with errors

- Incremental and interactive

- Enable live feedback and support for IDE features

- For more :

- Getting Started with Synopsys Euclide

# **Thank You**